Digilent 6003-410-000P-KIT User Manual

Page 65

XUP Virtex-II Pro Development System

65

UG069 (v1.0) March 8, 2005

Using System ACE Controllers for Non-Volatile Storage

R

Using System ACE Controllers for Non-Volatile Storage

In addition to programming the FPGA and storing bitstreams, the System ACE controller

can be used for general-purpose non-volatile storage. Each System ACE controller

provides an MPU interface to allow a microprocessor to access the attached CompactFlash

or IBM Microdrive, allowing this storage media to be used as a file system.

The MPU interface provides a useful means of monitoring the status of and controlling the

System ACE controller, as well as CompactFlash card READ/WRITE data. The MPU is not

required for normal operation, but when it is used, it provides numerous capabilities. This

interface enables communication between an MPU device, a CompactFlash card, and the

FPGA target system.

The MPU interface is composed of a set of registers that provide a means for

communicating with CompactFlash control logic, configuration control logic, and other

resources in the System ACE controller. This interface can be used to read the identity of a

CompactFlash device and read/write sectors from or to a CompactFlash device.

The MPU interface can also be used to control configuration flow. It enables monitoring of

the configuration status and error conditions. The MPU interface can be used to delay

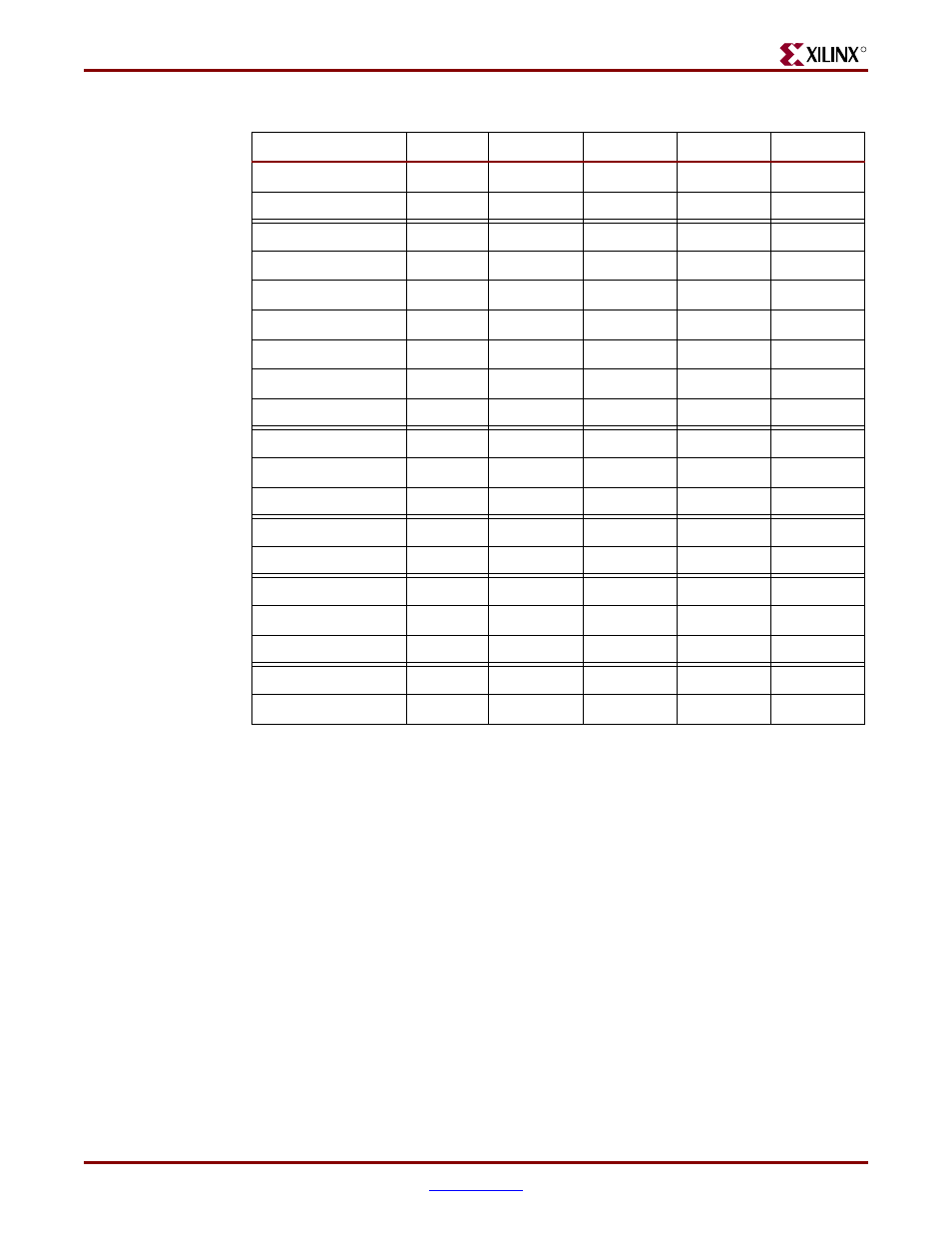

TX_CLOCK

I

D3

LVTTL

–

–

TX_ENABLE

O

C4

LVTTL

8 mA

SLOW

RX_DATA[0]

I

K6

LVTTL

–

–

RX_DATA[1]

I

K5

LVTTL

–

–

RX_DATA[2]

I

J1

LVTTL

–

–

RX_DATA[3]

I

K1

LVTTL

–

–

RX_DATA_VALID

I

M7

LVTTL

–

–

RX_ERROR

I

J2

LVTTL

–

–

RX_CLOCK

I

M8

LVTTL

–

–

ENET_RESET_Z

O

G6

LVTTL

8 mA

SLOW

CARRIER_SENSE

I

C5

LVTTL

–

–

COL_DETECT

I

D5

LVTTL

–

–

ENET_SLEW0

O

B3

LVTTL

8 mA

SLOW

ENET_SLEW1

O

A3

LVTTL

8 mA

SLOW

MDIO

I/O

M5

LVTTL

8 mA

SLOW

MDC

O

M6

LVTTL

8 mA

SLOW

MDINIT_Z

I

G5

LVTTL

–

–

PAUSE

O

J4

LVTTL

8 mA

SLOW

SSN_DATA

I

J3

LVTTL

8 mA

SLOW

Table 2-19:

10/100 ETHERNET Connections (Continued)

Signal

Direction

FPGA Pin

I/O Type

Drive

Slew