Teledyne LeCroy PeRT3 Phoenix System User Manual

Page 62

60

Teledyne LeCroy

System Control Ribbon ‐‐ Channel Tabs

High frequency SJ and low frequency SJ can be used in any combination (and also with

random jitter) to produce complex yet reproducible jitter scenarios for testing of serial

data devices.

The frequency range of Low Frequency Sinusoidal Jitter is typically below the frequency

that is tracked out by standard PLLs. This means that typical devices can tolerate Low

Frequency Sinusoidal Jitter in excess of several unit intervals. It also means that

measurement and calibration of sinusoidal jitter at low frequencies require techniques

that take into account the effects of any PLL used to recover the data.

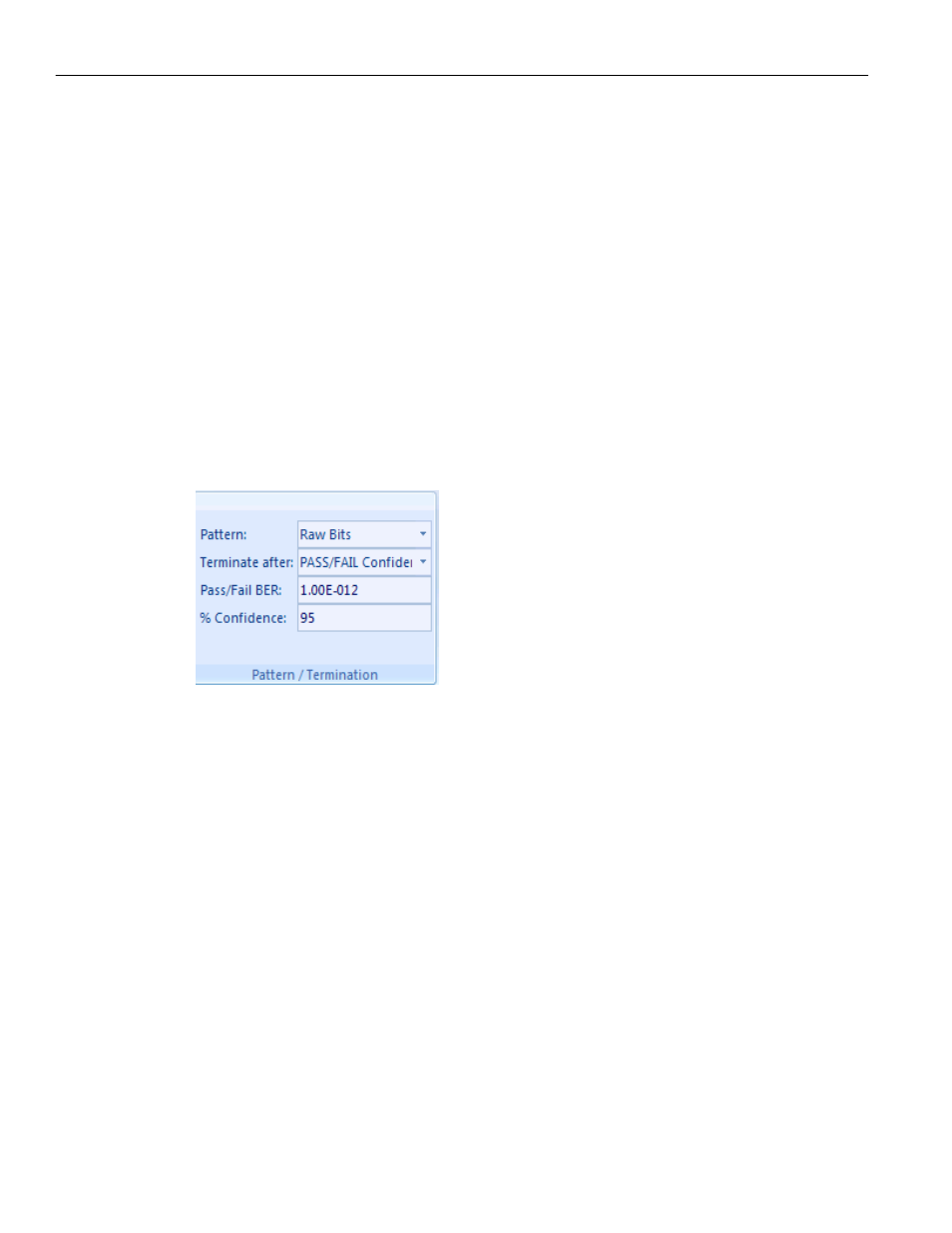

Pattern/Termination

The Pattern/Termination panel allows the user to define the test pattern to be used

during the test, and to define the termination conditions for ending the test.

The Pattern is selected from the drop‐down menu, and can be any pattern that is

supplied with the system or has been created by the user using the Pattern Editor (see

later section).

Figure 6.21: Patter Termination Panel

The Terminate after field allows the user to select the conditions that will terminate the

test. There are fields below the Terminate after field which change depending on the

selection made in the Terminate after field. You can choose from the following options:

Run Forever

If Run Forever is selected, the test will continue until the user stops the test using the

Suspend or Stop buttons in the Master Controls.

Max Bit Count

If Max Bit Count is selected, the test will continue until the number of Gbits of data

specified in the Max GBits field has been exceeded. Under nominal conditions, this is

equivalent to a fixed time period (that will depend on the data rate selected or

negotiated by the system). In the marginal test case where the device under test

sporadically loses and regains signal lock, it may take longer to achieve the expected bit

count than the equivalent time period. In the event the device totally loses signal lock

and stops transmitting, the test case will eventually time out even if the maximum bit

count is never achieved.