Atmega169v/l – Rainbow Electronics Atmega169L User Manual

Page 89

89

ATmega169V/L

2514A–AVR–08/02

Note:

1. The CTC0 and PWM0 bit definition names are now obsolete. Use the WGM01:0 def-

initions. However, the functionality and location of these bits are compatible with

previous versions of the timer.

• Bit 5:4 – COM01:0: Compare Match Output Mode

These bits control the Output Compare pin (OC0A) behavior. If one or both of the

COM0A1:0 bits are set, the OC0A output overrides the normal port functionality of the

I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit cor-

responding to the OC0A pin must be set in order to enable the output driver.

When OC0A is connected to the pin, the function of the COM0A1:0 bits depends on the

WGM01:0 bit setting. Table 50 shows the COM0A1:0 bit functionality when the

WGM01:0 bits are set to a normal or CTC mode (non-PWM).

Table 51 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast

PWM mode.

Note:

1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case,

the compare match is ignored, but the set or clear is done at TOP. See “Fast PWM

Mode” on page 84 for more details.

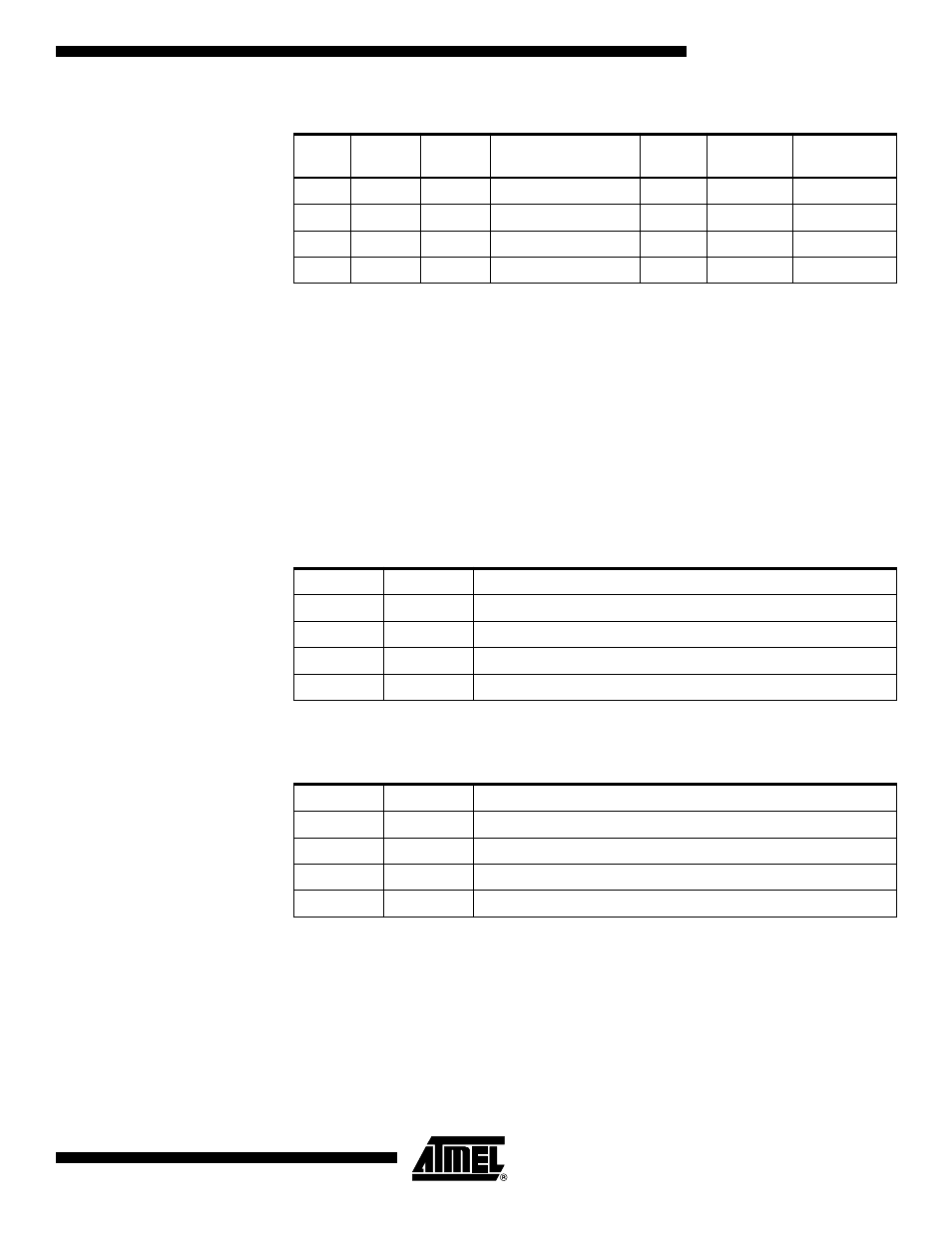

Table 49. Waveform Generation Mode Bit Description

(1)

Mode

WGM01

(CTC0)

WGM00

(PWM0)

Timer/Counter

Mode of Operation

TOP

Update of

OCR0A at

TOV0 Flag

Set on

0

0

0

Normal

0xFF

Immediate

MAX

1

0

1

PWM, Phase Correct

0xFF

TOP

BOTTOM

2

1

0

CTC

OCR0A

Immediate

MAX

3

1

1

Fast PWM

0xFF

TOP

MAX

Table 50. Compare Output Mode, non-PWM Mode

COM01

COM00

Description

0

0

Normal port operation, OC0A disconnected.

0

1

Toggle OC0A on compare match

1

0

Clear OC0A on compare match

1

1

Set OC0A on compare match

Table 51. Compare Output Mode, Fast PWM Mode

(1)

COM01

COM00

Description

0

0

Normal port operation, OC0A disconnected.

0

1

Reserved

1

0

Clear OC0A on compare match, set OC0A at TOP

1

1

Set OC0A on compare match, clear OC0A at TOP