Atmega169v/l – Rainbow Electronics Atmega169L User Manual

Page 222

222

ATmega169V/L

2514A–AVR–08/02

• Bit 3 – Res: Reserved Bit

This bit is reserved bit in the ATmega169 and will always read as zero.

• Bits 2:0 – LCDCD2:0: LCD Clock Divide 2, 1, and 0

The LCDCD2:0 bits determine division ratio in the clock divider. The various selections

are shown in Table 97. This Clock Divider gives extra flexibility in frame rate selection.

The frame frequency can be calculated by the following equation:

Where:

N = prescaler divider (16, 64, 128, 256, 512, 1024, 2048, or 4096).

K = 8 for duty = 1/4, 1/2, and static.

K = 6 for duty = 1/3.

This is a very flexible scheme, and users are encouraged to calculate their own table to

investigate the possible frame rates from the formula above. Note when using 1/3 duty

the frame rate is increased with 33% when Frame Rate Register is constant. Example of

frame rate calculation is shown in Table 98.

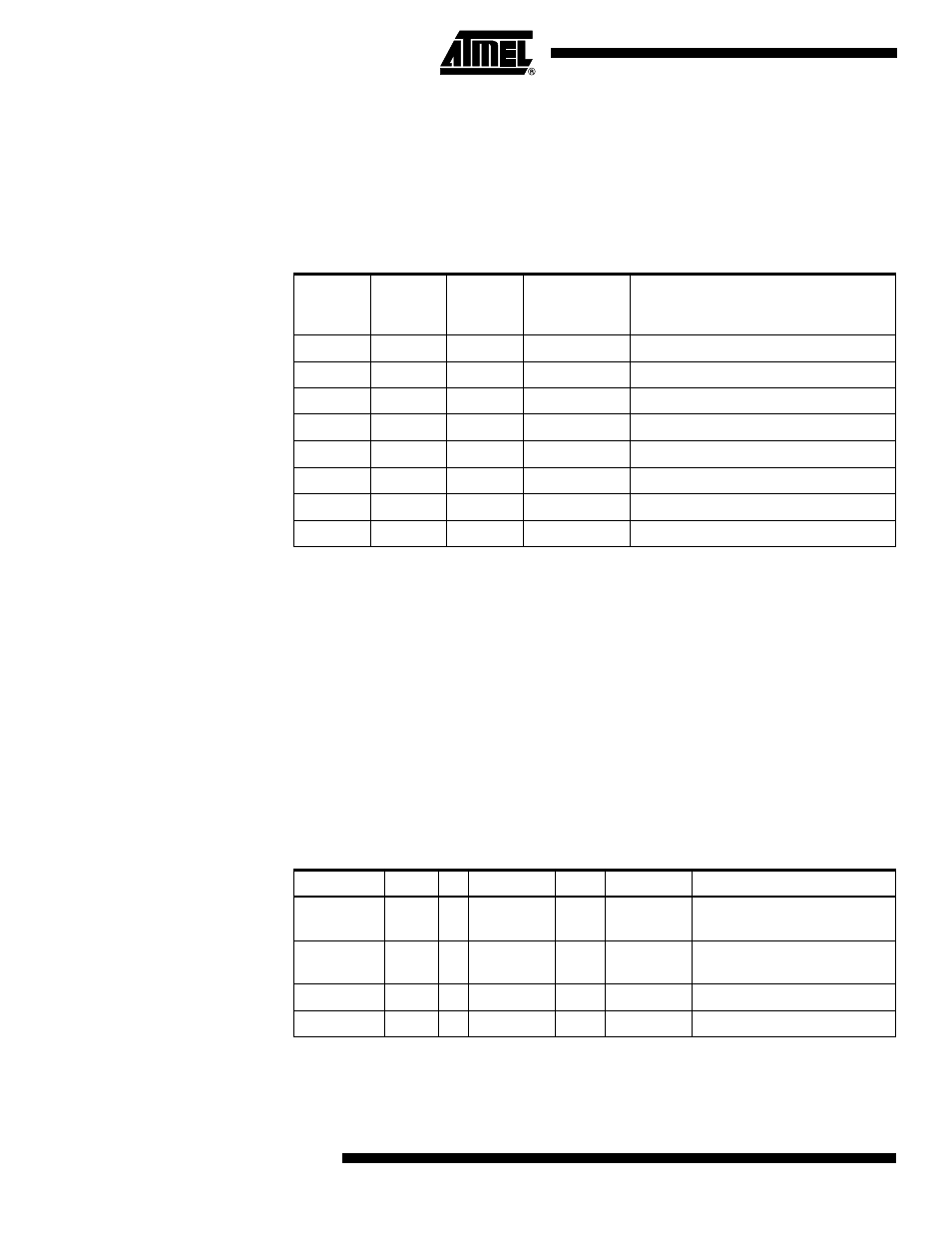

Table 97. LCD Clock Divide

LCDCD2

LCDCD1

LCDCD0

Output from

Prescaler

Divided by:

clk

LCD

= 32.768 kHz, N = 16, and Duty

= 1/4, gives a frame rate of:

0

0

0

1

256 Hz

0

0

1

2

128 Hz

0

1

0

3

85.3 Hz

0

1

1

4

64 Hz

1

0

0

5

51.2 Hz

1

0

1

6

42.7 Hz

1

1

0

7

36.6 Hz

1

1

1

8

32 Hz

Table 98. Example of frame rate calculation

ckl

LCD

duty

K

LCDPS2:0

N

LCDCS2:0

Frame Rate

4 MHz

1/4

8

6

2048

3

4000000/(8*2048*(1+3)) =

61 Hz

4 MHz

1/3

6

6

2048

3

4000000/(6*2048*(1+3)) =

81 Hz

32.768 kHz

Static

8

0

16

0

32768/(8*16*(1+0)) = 256 Hz

32.768 kHz

1/2

8

0

16

4

32768/(8*16*(1+4)) = 51 Hz

f

fram e

f

c lk

LC D

K N

1

LCDCD

+

(

)

⋅ ⋅

(

)

---------------------------------------------------------

=