Texas Instruments TMS320C645X User Manual

Page 92

www.ti.com

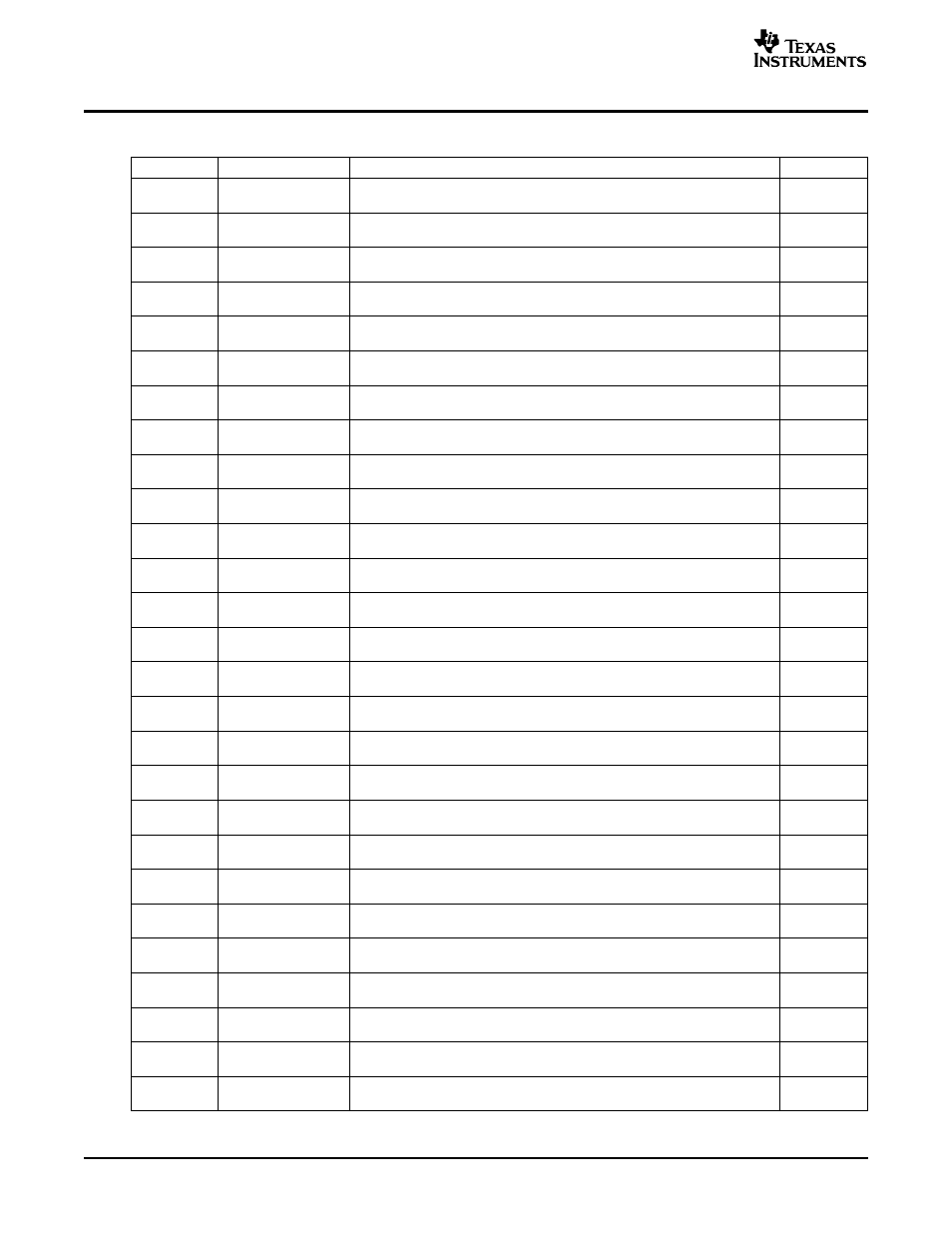

SRIO Registers

Table 28. Serial Rapid IO (SRIO) Registers (continued)

Offset

Acronym

Register Description

Section

0x0584

QUEUE1_TXDMA_C

Queue Transmit DMA Completion Pointer Register 1

P

0x0588

QUEUE2_TXDMA_C

Queue Transmit DMA Completion Pointer Register 2

P

0x058C

QUEUE3_TXDMA_C

Queue Transmit DMA Completion Pointer Register 3

P

0x0590

QUEUE4_TXDMA_C

Queue Transmit DMA Completion Pointer Register 4

P

0x0594

QUEUE5_TXDMA_C

Queue Transmit DMA Completion Pointer Register 5

P

0x0598

QUEUE6_TXDMA_C

Queue Transmit DMA Completion Pointer Register 6

P

0x059C

QUEUE7_TXDMA_C

Queue Transmit DMA Completion Pointer Register 7

P

0x05A0

QUEUE8_TXDMA_C

Queue Transmit DMA Completion Pointer Register 8

P

0x05A4

QUEUE9_TXDMA_C

Queue Transmit DMA Completion Pointer Register 9

P

0x05A8

QUEUE10_TXDMA_

Queue Transmit DMA Completion Pointer Register 10

CP

0x05AC

QUEUE11_TXDMA_

Queue Transmit DMA Completion Pointer Register 11

CP

0x05B0

QUEUE12_TXDMA_

Queue Transmit DMA Completion Pointer Register 12

CP

0x05B4

QUEUE13_TXDMA_

Queue Transmit DMA Completion Pointer Register 13

CP

0x05B8

QUEUE14_TXDMA_

Queue Transmit DMA Completion Pointer Register 14

CP

0x05BC

QUEUE15_TXDMA_

Queue Transmit DMA Completion Pointer Register 15

CP

0x0600

QUEUE0_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 0

DP

0x0604

QUEUE1_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 1

DP

0x0608

QUEUE2_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 2

DP

0x060C

QUEUE3_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 3

DP

0x0610

QUEUE4_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 4

DP

0x0614

QUEUE5_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 5

DP

0x0618

QUEUE6_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 6

DP

0x061C

QUEUE7_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 7

DP

0x0620

QUEUE8_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 8

DP

0x0624

QUEUE9_RXDMA_H

Queue Receive DMA Head Descriptor Pointer Register 9

DP

0x0628

QUEUE10_RXDMA_

Queue Receive DMA Head Descriptor Pointer Register 10

HDP

0x062C

QUEUE11_RXDMA_

Queue Receive DMA Head Descriptor Pointer Register 11

HDP

92

Serial RapidIO (SRIO)

SPRU976 – March 2006