Texas Instruments TMS320C645X User Manual

Page 102

www.ti.com

SRIO Registers

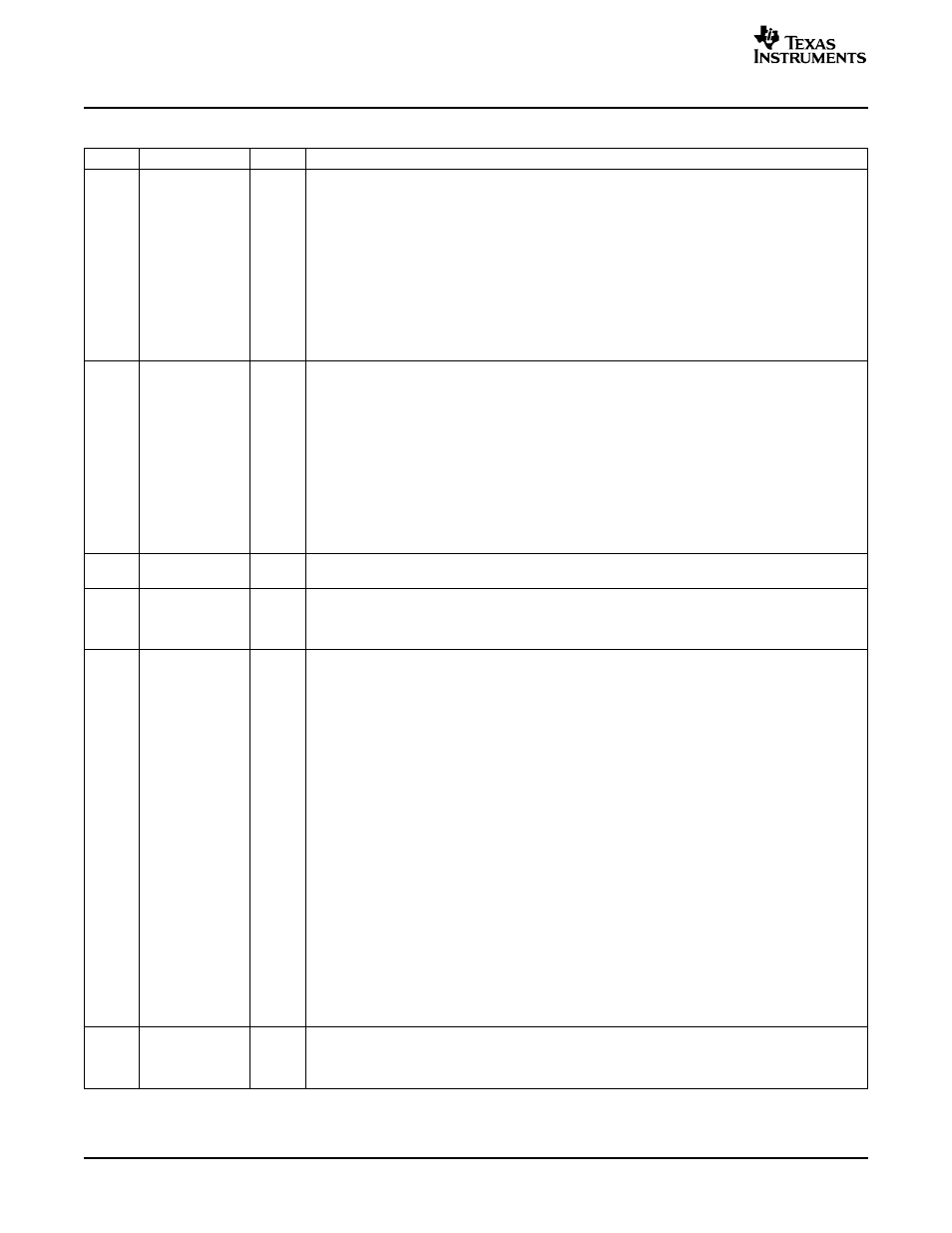

Table 31. Peripheral Settings Control Register (PER_SET_CNTL) Field Descriptions (continued)

Bit

Field

Value

Description

17-15

TX_PRI1_WM

Transmit credit threshold. Sets the required number of logical layer TX buffers needed to send

priority 1 packets across the UDI interface. This is valid for all ports in 1X mode only.

Required buffer count for transmit credit threshold 1 value TX_PRI1_WM:

•

000

→

8, 7, 6, 5, 4, 3, 2, 1

•

001

→

8, 7, 6, 5, 4, 3, 2

•

010

→

8, 7, 6, 5, 4, 3

•

011

→

8, 7, 6, 5, 4

•

100

→

8, 7, 6, 5

•

101

→

8, 7, 6

•

110

→

8, 7

•

111

→

8

14-12

TX_PRI0_WM

Transmit credit threshold. Sets the required number of logical layer TX buffers needed to send

priority 0 packets across the UDI interface. This is valid for all ports in 1X mode only.

Required buffer count for transmit credit threshold 0 value TX_PRI0_WM:

•

000

→

8, 7, 6, 5, 4, 3, 2, 1

•

001

→

8, 7, 6, 5, 4, 3, 2

•

010

→

8, 7, 6, 5, 4, 3

•

011

→

8, 7, 6, 5, 4

•

100

→

8, 7, 6, 5

•

101

→

8, 7, 6

•

110

→

8, 7

•

111

→

8

11-9

CBA_TRANS_PR

VBUS transaction priority. 000b – Highest Priority

…

111b – Lowest Priority.

I

8

1X_MODE

This register bit determines the UDI buffering setup (priority versus port).

0b

UDI buffers are priority based

1b

UDI buffers are port based. This mode must be selected when using more than one 1X port

7-4

PRESCALER_SE

Internal frequency prescaler, used to drive the request to response timers. These 4 bits are the

LECT

prescaler reload value allowing division of the DMA clock by a range from 1 up to 16. Setting

should reflect the device DMA frequency.

0000b

Sets the internal clock frequency Min 44.7 and Max 89.5

0001b

Sets the internal clock frequency Min 89.5 and Max 179.0

0010b

Sets the internal clock frequency Min 134.2 and Max 268.4

0011b

Sets the internal clock frequency Min 180.0 and Max 360.0

0100b

Sets the internal clock frequency Min 223.7 and Max 447.4

0101b

Sets the internal clock frequency Min 268.4 and Max 536.8

0110b

Sets the internal clock frequency Min 313.2 and Max 626.4

0111b

Sets the internal clock frequency Min 357.9 and Max 715.8

1000b

sets the internal clock frequency Min 402.7 and Max 805.4

1001b

Sets the internal clock frequency Min 447.4 and Max 894.8

1010b

Sets the internal clock frequency Min 492.1 and Max 984.2

1011b

Sets the internal clock frequency Min 536.9 and Max 1073.8

1100b

Sets the internal clock frequency Min 581.6 and Max 1163.2

1101b

Sets the internal clock frequency Min 626.3 and Max 1252.6

1110b

Sets the internal clock frequency Min 671.1 and Max 1342.2

1111b

Sets the internal clock frequency Min 715.8 and Max 1431.6

3

ENPLL4

Drives SERDES Macro 4 PLL Enable signal

0b

Disables macro 4 PLL

1b

Enables macro 4 PLL

102

Serial RapidIO (SRIO)

SPRU976 – March 2006