79 port response time-out control csr (sp_rt_ctl), Sp_rt_ctl), Section 5.79 – Texas Instruments TMS320C645X User Manual

Page 181

www.ti.com

5.79

Port Response Time-Out Control CSR (SP_RT_CTL)

SRIO Registers

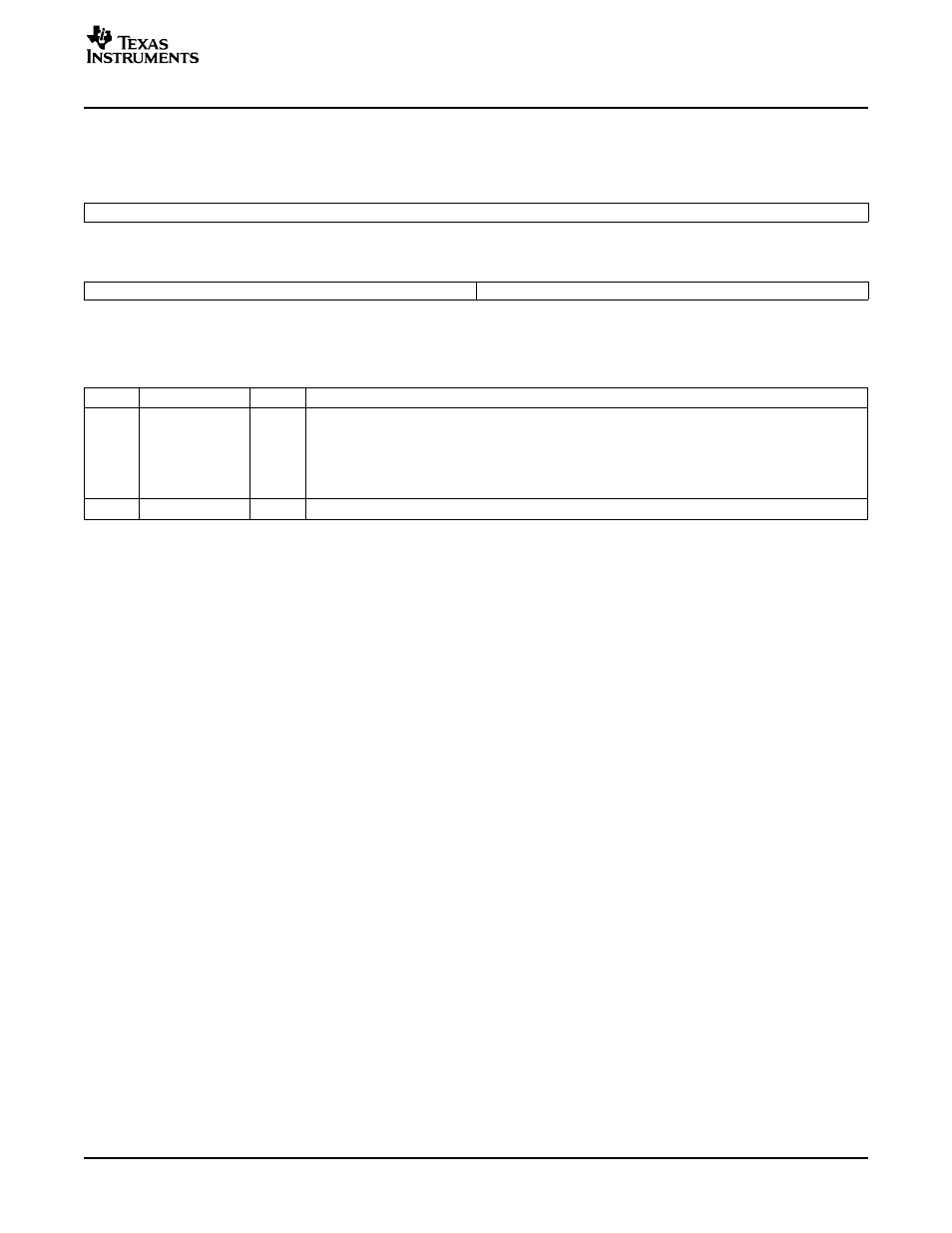

Figure 135. Port Response Time-Out Control CSR (SP_RT_CTL)

31-16

TIMEOUT_VALUE

RW-0xFFFFFF

LEGEND: R = Read only; -n = value after reset

15-8

7-0

TIMEOUT_VALUE

Reserved

RW-0xFFFFFF

R-0x00

LEGEND: R = Read only; -n = value after reset

Table 109. Port Response Time-Out Control CSR (SP_RT_CTL) Field Descriptions

Bit

Field

Value

Description

31-8

TIMEOUT_VALU

Timeout value for all ports on the device. This timeout is for sending a packet to receiving the

E

corresponding response packet. Max value represents 3-6 seconds. The timeout duration can be

expressed as: Timeout = 15 * ((Prescale value + 1) * DMA clock period * Timeout Value); where

Prescale value is set in 0x0020 PSCR and the Timeout value is the decimal representation of this

register value. Example: 400Mhz DMA, Prescalar 0100b, Timeout Value FFFFFFh; Timeout

duration = 15*(4+1)*2.5nS*16777216 = 3.15s.

7-0

Reserved

Reserved

SPRU976 – March 2006

Serial RapidIO (SRIO)

181