Options – Texas Instruments TMS320C645X User Manual

Page 81

www.ti.com

Interrupt Conditions

The interrupt conditions are programmable to select the interrupt output that will be driven. Each condition

is independently programmable to use any of the interrupt destinations supported by the device. For

example, a quad core device may support four CPU servicing interrupt destinations, one per core

(INTDST0 for Core0, INTDST1 for Core1, INTDST2 for Core2, and INTDST3 for Core3). In addition,

INTDST4 may be globally routed to all cores and provide notification of a change in the Error Status

interrupt ICSR. INTDST5 may be globally routed to all cores and provide notification of a change in the

Device Reset interrupt ICSR. The routing defaults are shown below.

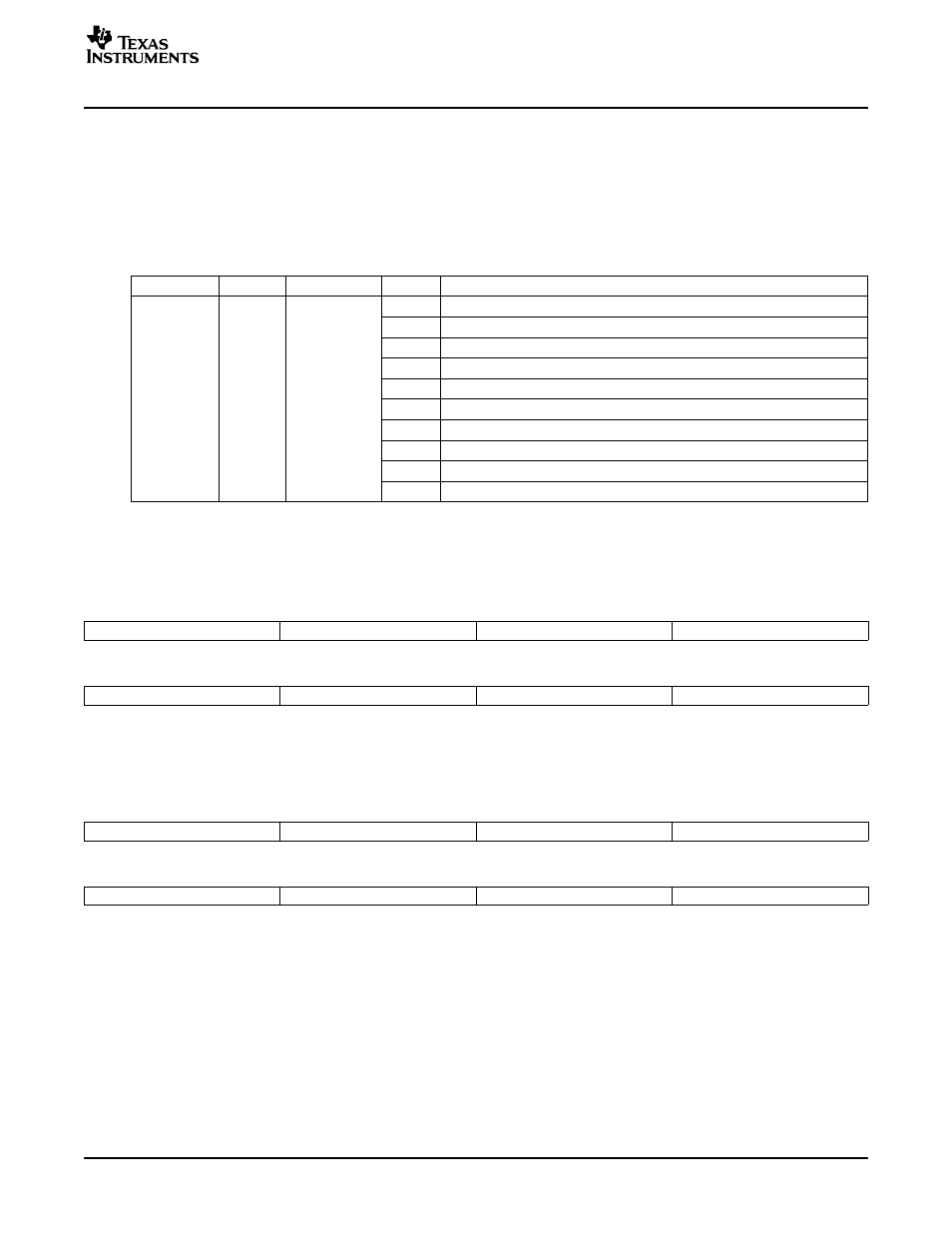

Table 27. Interrupt Condition Routing Options

Field

Access

Reset Value

Value

Function

ICRx

R

0000b

0000b

Routed to INTDST0

0001b

Routed to INTDST1

0010b

Routed to INTDST2

0011b

Routed to INTDST3

0100b

Routed to INTDST4

0101b

Routed to INTDST5

0110b

Routed to INTDST6

0111b

Routed to INTDST7

1111b

No interrupt destination, interrupt source disabled

other

Reserved

Figure 51. Doorbell 0 Interrupt Condition Routing Registers

DOORBELL0_ICRR (Address Offset 0x280)

31

28

27

24

23

20

19

16

ICR7

ICR6

ICR5

ICR4

R/W-0000

R/W-0000

R/W-0000

R/W-0000

15

12

11

8

7

4

3

0

ICR3

ICR2

ICR1

ICR0

R/W-0000

R/W-0000

R/W-0000

R/W-0000

LEGEND: R = Read, W = Write, n = value at reset

DOORBELL0_ICRR2 (Address Offset 0x284)

31

28

27

24

23

20

19

16

ICR15

ICR14

ICR13

ICR12

R/W-0000

R/W-0000

R/W-0000

R/W-0000

15

12

11

8

7

4

3

0

ICR11

ICR10

ICR9

ICR8

R/W-0000

R/W-0000

R/W-0000

R/W-0000

LEGEND: R = Read, W = Write, n = value at reset

Other ICRRs have the same bit field map, with the following addresses:

•

DOORBELL1_ICRR and DOORBELL1_ICCR2 (Address Offset 0x0290 and 0x0294)

•

DOORBELL2_ICRR and DOORBELL2_ICRR2 (Address Offset 0x02A0 and 0x02A4)

•

DOORBELL3_ICRR and DOORBELL3_ICRR2 (Address Offset 0x02B0 and 0x02B4)

•

RX CPPI_ICRR and RX CPPI_ICRR2 (Address Offset 0x02C0 and 0x02C4)

•

TX CPPI_ICRR and TX CPPI_ICRR2 (Address Offset 0x02D0 and 0x02D4)

SPRU976 – March 2006

Serial RapidIO (SRIO)

81