Architecture, Overview – Texas Instruments TMS320C645X User Manual

Page 16

www.ti.com

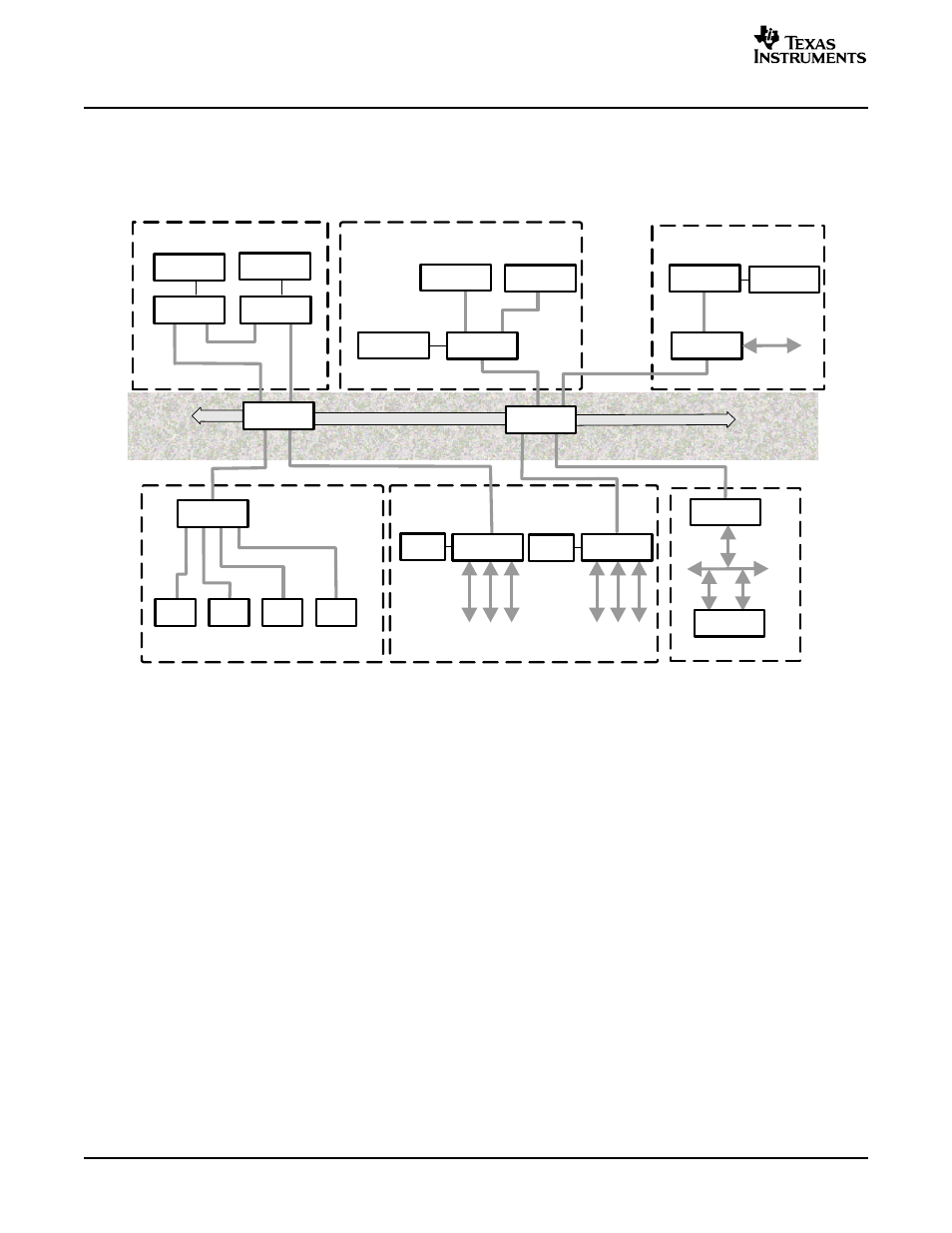

Host Subsystem

I/O Control Subsystem

DSP Farm

TDM,GMII, Utopia

Communications Subsystem

PCI Subsystem

InfiniBand

HCA

™

To System Area

Network

Memory

Memory

Memory

Memory

RapidIO

RapidIO

RapidIO

RapidIO

RapidIO

Backplane

PCI

RapidIO

RapidIO

RapidIO

RapidIO

Switch

Control

Processor

IO

Processor

RapidIO to

InfiniBand

RapidIO

Switch

RapidIO

Switch

Legacy

Comm

Processor

RapidIO

Switch

RapidIO to

PCI Bridge

ASIC/FPGA

Memory

Memory

Host

Processor

Host

Processor

DSP

DSP

DSP

DSP

Comm

Processor

Overview

1.1.2

RapidIO Interconnect Architecture

The interconnect architecture is defined as a packet switched protocol independent of a physical layer

implementation.

illustrates the interconnection system.

Figure 2. RapidIO Interconnect Architecture

(1)

InfiniBand™ is a trademark of the InfiniBand Trade Association.

1.1.3

1x/4x LP-Serial

Currently, there are two physical layer specifications recognized by the RapidIO Trade Association: 8/16

LP-LVDS and 1X/4X LP-Serial. The 8/16 LP-LVDS specification is a point-to-point synchronous clock

sourcing DDR interface. The 1X/4X LP-Serial specification is a point-to-point, AC coupled, clock recovery

interface. The two physical layer specifications are not compatible.

SRIO complies with the 1X/4X LP-Serial specification. The serializer/deserializer (SERDES) technology in

SRIO also aligns with that specification.

The 1X/4X LP-Serial specification currently covers three frequency points: 1.25, 2.5, and 3.125 Gbps. This

defines the total bandwidth of each differential pair of I/O signals. An 8b/10b encoding scheme ensures

ample data transitions for the clock recovery circuits. Due to the 8b/10b encoding overhead, the effective

data bandwidth per differential pair is 1.0, 2.0, and 2.5 Gbps respectively. Serial RapidIO only specifies

these rates for both the 1X and 4X ports. A 1X port is defined as 1 TX and 1 RX differential pair. A 4X port

is a combination of four of these pairs. This document describes a 4X RapidIO port that can also be

configured as four 1X ports, thus providing a scalable interface capable of supporting a data bandwidth of

1 to 10 Gbps.

16

Serial RapidIO (SRIO)

SPRU976 – March 2006