Texas Instruments TMS320C645X User Manual

Page 91

www.ti.com

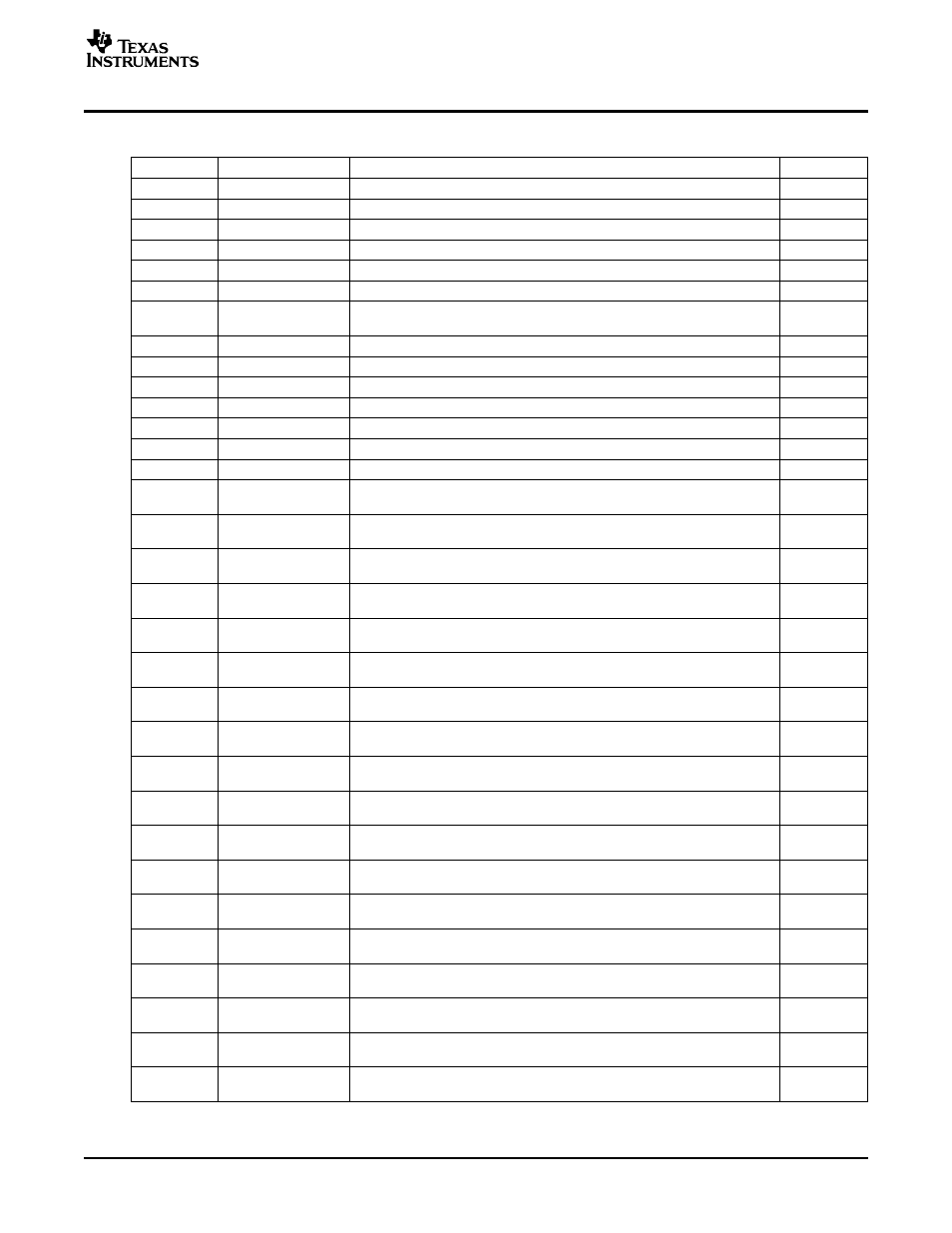

SRIO Registers

Table 28. Serial Rapid IO (SRIO) Registers (continued)

Offset

Acronym

Register Description

Section

0x0444

LSU3_REG1

LSU3 Control Register 1

0x0448

LSU3_REG2

LSU3 Control Register 2

0x044C

LSU3_REG3

LSU3 Control Register 3

0x0450

LSU3_REG4

LSU3 Control Register 4

0x0454

LSU3_REG5

LSU3 Control Register 5

0x0458

LSU3_REG6

LSU3 Control Register 6

0x045C

LSU3_FLOW_MASK

Core 2 LSU Congestion Control Flow Mask Register

S2

0x0460

LSU4_REG0

LSU4 Control Register 0

0x0464

LSU4_REG1

LSU4 Control Register 1

0x0468

LSU4_REG2

LSU4 Control Register 2

0x046C

LSU4_REG3

LSU4 Control Register 3

0x0470

LSU4_REG4

LSU4 Control Register 4

0x0474

LSU4_REG5

LSU4 Control Register 5

0x0478

LSU4_REG6

LSU4 Control Register 6

0x047C

LSU4_FLOW_MASK

Core 3 LSU Congestion Control Flow Mask Register

S3

0x0500

QUEUE0_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 0

DP

0x0504

QUEUE1_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 1

DP

0x0508

QUEUE2_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 2

DP

0x050C

QUEUE3_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 3

DP

0x0510

QUEUE4_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 4

DP

0x0514

QUEUE5_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 5

DP

0x0518

QUEUE6_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 6

DP

0x051C

QUEUE7_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 7

DP

0x0520

QUEUE8_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 8

DP

0x0524

QUEUE9_TXDMA_H

Queue Transmit DMA Head Descriptor Pointer Register 9

DP

0x0528

QUEUE10_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 10

HDP

0x052C

QUEUE11_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 11

HDP

0x0530

QUEUE12_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 12

HDP

0x0534

QUEUE13_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 13

HDP

0x0538

QUEUE14_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 14

HDP

0x053C

QUEUE15_TXDMA_

Queue Transmit DMA Head Descriptor Pointer Register 15

HDP

0x0580

QUEUE0_TXDMA_C

Queue Transmit DMA Completion Pointer Register 0

P

SPRU976 – March 2006

Serial RapidIO (SRIO)

91