56 receive cppi control register (rx_cppi_cntl), Rx_cppi_cntl), Descriptions – Texas Instruments TMS320C645X User Manual

Page 158: Section 5.56

www.ti.com

5.56

Receive CPPI Control Register (RX_CPPI_CNTL)

SRIO Registers

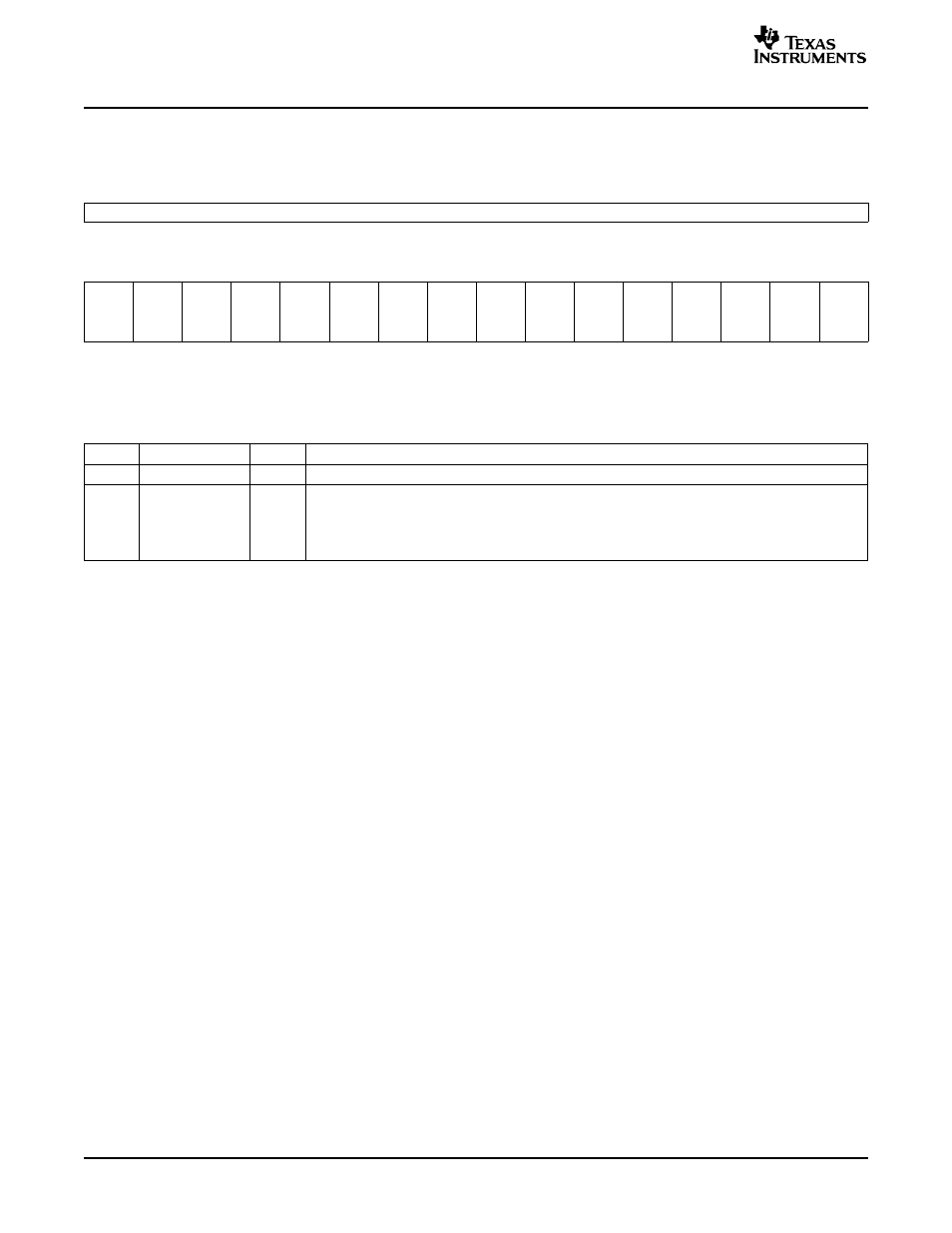

Figure 112. Receive CPPI Control Register (RX_CPPI_CNTL)

31-16

Reserved

R-0x00

LEGEND: R = Read only; -n = value after reset

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

QUEU

E15_I

E14_I

E13_I

E12_I

E11_I

E10_I

E9_IN

E8_IN

E7_IN

E6_IN

E5_IN

E4_IN

E3_IN

E2_IN

E1_IN

E0_IN

N_OR

N_OR

N_OR

N_OR

N_OR

N_OR

_ORD

_ORD

_ORD

_ORD

_ORD

_ORD

_ORD

_ORD

_ORD

_ORD

DER

DER

DER

DER

DER

DER

ER

ER

ER

ER

ER

ER

ER

ER

ER

ER

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

RW-

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

LEGEND: R = Read only; -n = value after reset

Table 86. Receive CPPI Control Register (RX_CPPI_CNTL) Field Descriptions

Bit

Field

Value

Description

31-16

Reserved

Reserved

15-0

QUEUEn_IN_OR

Queuen In Order (QUEUE(0-15)_IN_ORDER)

DER (0-15)

0b

Allows out-of-order message

1b

Only allows in-order messages. Used for applications with dedicated source-destination flows.

Serial RapidIO (SRIO)

158

SPRU976 – March 2006