Texas Instruments TMS320C645X User Manual

Page 89

www.ti.com

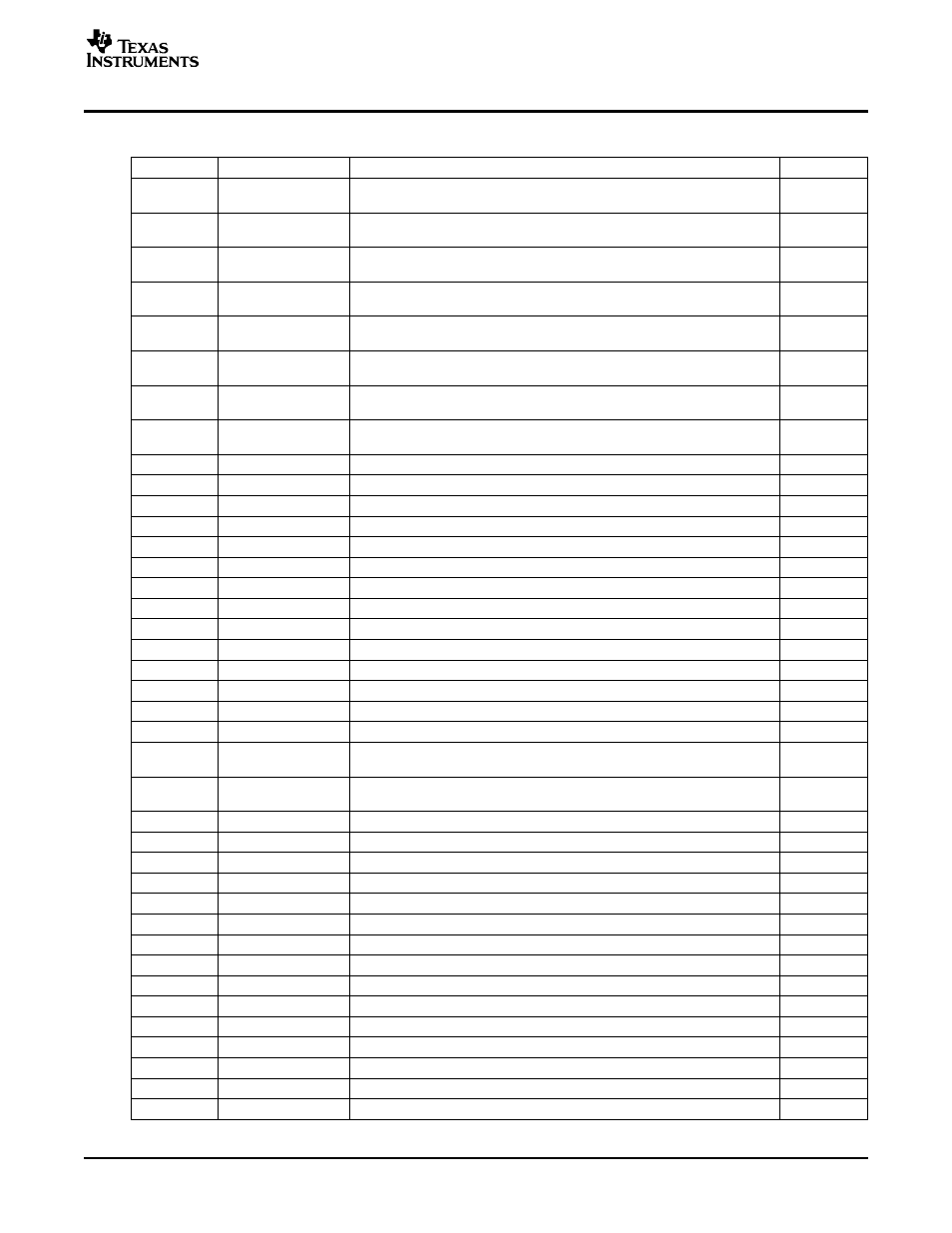

SRIO Registers

Table 28. Serial Rapid IO (SRIO) Registers (continued)

Offset

Acronym

Register Description

Section

0x0110

SERDES_CFGTX0_

SERDES Transmit Channel Configuration Register 0

CNTL

0x0114

SERDES_CFGTX1_

SERDES Transmit Channel Configuration Register 1

CNTL

0x0118

SERDES_CFGTX2_

SERDES Transmit Channel Configuration Register 2

CNTL

0x011C

SERDES_CFGTX3_

SERDES Transmit Channel Configuration Register 3

CNTL

0x0120

SERDES_CFG0_CN

SERDES Macro Configuration Register 0

TL

0x0124

SERDES_CFG1_CN

SERDES Macro Configuration Register 1

TL

0x0128

SERDES_CFG2_CN

SERDES Macro Configuration Register 2

TL

0x012C

SERDES_CFG3_CN

SERDES Macro Configuration Register 3

TL

0x0200

DOORBELL0_ICSR

DOORBELL Interrupt Status Register 0

0x0208

DOORBELL0_ICCR

DOORBELL Interrupt Clear Register 0

0x0210

DOORBELL1_ICSR

DOORBELL Interrupt Status Register 1

0x0218

DOORBELL1_ICCR

DOORBELL Interrupt Clear Register 1

0x0220

DOORBELL2_ICSR

DOORBELL Interrupt Status Register 2

0x0228

DOORBELL2_ICCR

DOORBELL Interrupt Clear Register 2

0x0230

DOORBELL3_ICSR

DOORBELL Interrupt Status Register 3

0x0238

DOORBELL3_ICCR

DOORBELL Interrupt Clear Register 3

0x0240

RX_CPPI_ICSR

RX CPPI Interrupt Status Register

0x0248

RX_CPPI_ICCR

RX CPPI Interrupt Clear Register

0x0250

TX_CPPI_ICSR

TX CPPI Interrupt Status Register

0x0258

TX_CPPI_ICCR

TX CPPI Interrupt Clear Register

0x0260

LSU_ICSR

LSU Interrupt Status Register

0x0268

LSU _ICCR

LSU Interrupt Clear Register

0x0270

ERR_RST_EVNT_IC

Error, Reset, and Special Event Interrupt Status Register

SR

0x0278

ERR_RST_EVNT_IC

Error, Reset, and Special Event Interrupt Clear Register

CR

0x0280

DOORBELL0_ICRR

DOORBELL0 Interrupt Condition Routing Register (bits 0 to 7)

0x0284

DOORBELL0_ICRR2

DOORBELL 0 Interrupt Condition Routing Register 2 (bits 8 to 15)

0x0290

DOORBELL1_ICRR

DOORBELL1 Interrupt Condition Routing Register (bits 0 to 7)

0x0294

DOORBELL1_ICRR2

DOORBELL 1 Interrupt Condition Routing Register 2 (bits 8 to 15)

0x02A0

DOORBELL2_ICRR

DOORBELL2 Interrupt Condition Routing Register (bits 0 to 7)

0x02A4

DOORBELL2_ICRR2

DOORBELL 2 Interrupt Condition Routing Register 2 (bits 8 to 15)

0x02B0

DOORBELL3_ICRR

DOORBELL3 Interrupt Condition Routing Register (bits 0 to 7)

0x02B4

DOORBELL3_ICRR2

DOORBELL 3 Interrupt Condition Routing Register 2 (bits 8 to 15)

0x02C0

RX_CPPI _ICRR

Receive CPPI Interrupt Condition Routing Register (0 to 7)

0x02C4

RX_CPPI _ICRR2

Receive CPPI Interrupt Condition Routing Register (8 to 15)

0x02D0

TX_CPPI _ICRR

Transmit CPPI Interrupt Condition Routing Register (0 to 7)

0x02D4

TX_CPPI _ICRR2

Transmit CPPI Interrupt Condition Routing Register (8 to 15)

0x02E0

LSU_ICRR0

LSU Interrupt Condition Routing Register 0

0x02E4

LSU_ICRR1

LSU Interrupt Condition Routing Register 1

0x02E8

LSU_ICRR2

LSU Interrupt Condition Routing Register 2

SPRU976 – March 2006

Serial RapidIO (SRIO)

89