Err_attr_capt_dbg0), Descriptions, Section 5.96 – Texas Instruments TMS320C645X User Manual

Page 200

www.ti.com

5.96

Port n Attributes Error Capture CSR 0 (SPn_ERR_ATTR_CAPT_DBG0)

SRIO Registers

Each of the four ports is supported by a register of this type.

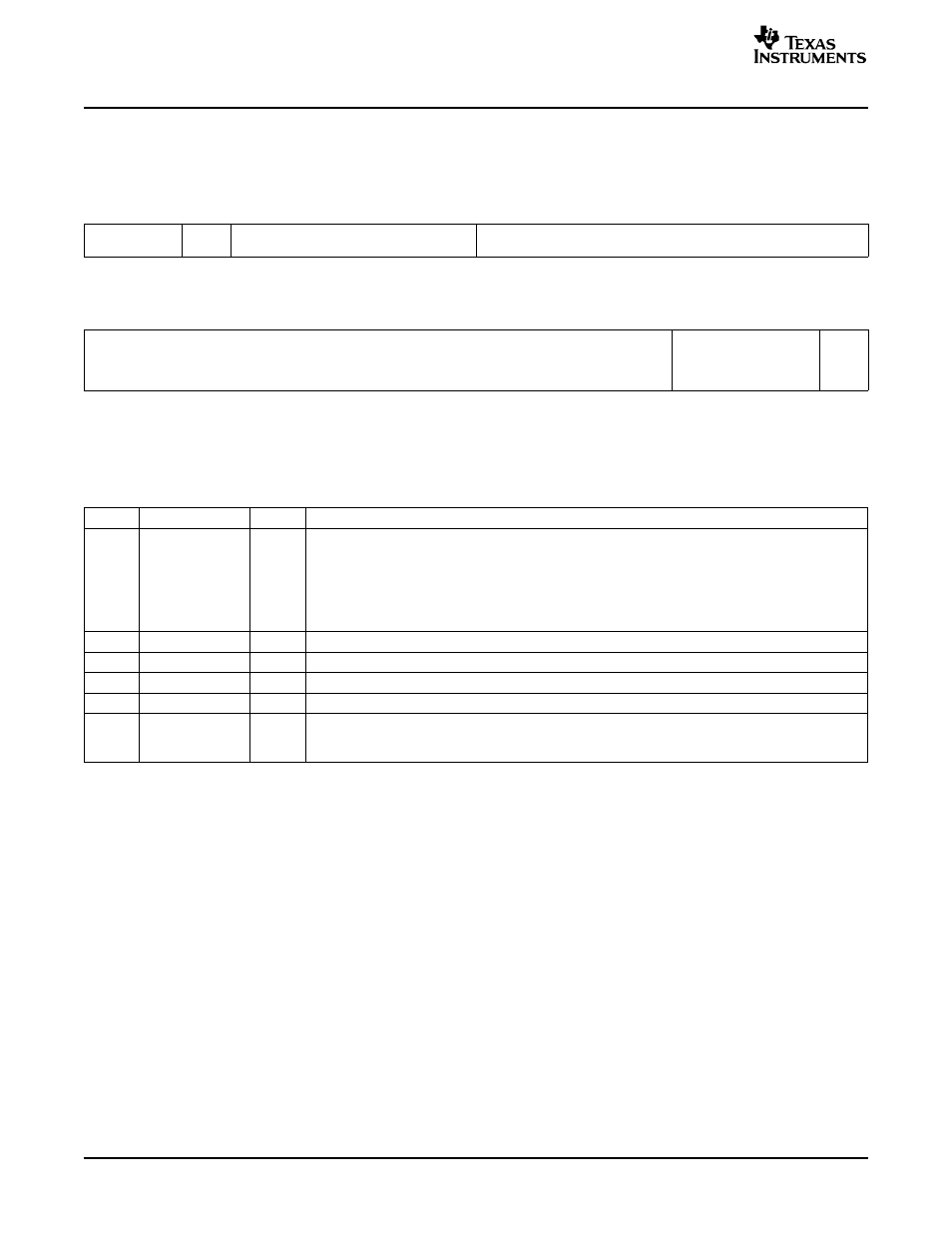

Figure 152. Port n Attributes Error Capture CSR 0 (SPn_ERR_ATTR_CAPT_DBG0)

31-30

29

28-24

23-16

INFO_TYPE

Reserv

ERROR_TYPE

IMP_SPECIFIC

ed

R-0x00

R-

R-0x00

R-0x00

0x00

LEGEND: R = Read only; -n = value after reset

15-4

3-1

0

IMP_SPECIFIC

Reserved

CAPT

URE_

VALID

_INFO

R-0x00

R-0x00

RC-

0x00

LEGEND: R = Read only; -n = value after reset

Table 126. Port n Attributes Error Capture CSR 0 (SPn_ERR_ATTR_CAPT_DBG0) Field

Descriptions

Bit

Field

Value

Description

31-30

INFO_TYPE

Type of information logged.

00

Packet

01

Control symbol (only error capture register 0 is valid)

10

Implementation specific (capture register contents are implementation specific)

11

Undefined (S-bit error), capture as if a packet (parallel physical layer only)

29

Reserved

Reserved

28-24

ERROR_TYPE

Encoded value of captured error bit in the Port n Error Detect Register

23-4

IMP_SPECIFIC

Implementation Dependent Error Information

3-1

Reserved

Reserved

0

CAPTURE_VALI

This bit is set by hardware to indicate that the Packet/control symbol capture registers contain valid

D_INFO

information. For control symbols, only capture register 0 will contain meaningful information. A

software write of 0 clears this bit and subsequently unlocks all capture registers of port n.

Serial RapidIO (SRIO)

200

SPRU976 – March 2006