Bits – Texas Instruments TMS320C645X User Manual

Page 84

www.ti.com

31

30

29

28

27

26

25

24

23

22

21

20

19

16

18

17

LSU

Error, reset and special event

Tx CPPI [15:0]

Rx CPPI [15:0]

ISDR bits:

15

ISDR bits:

14

13

12

11

6

8

10

9

7

5

4

3

2

0

1

Doorbell 0 [15:0]

Doorbell 1 [15:0]

Doorbell 3 [15:0]

Doorbell 2 [15:0]

29

29

29

29

29

29

29

29

Interrupt Status

Decode Registers

INTDST0

INTDST1

INTDST2

INTDST3

INTDST4

INTDST5

INTDST6

INTDST7

TX CPPI ICRR

TX CPPI ICRR

TX CPPI ICSR

RX CPPI ICSR

2

2

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

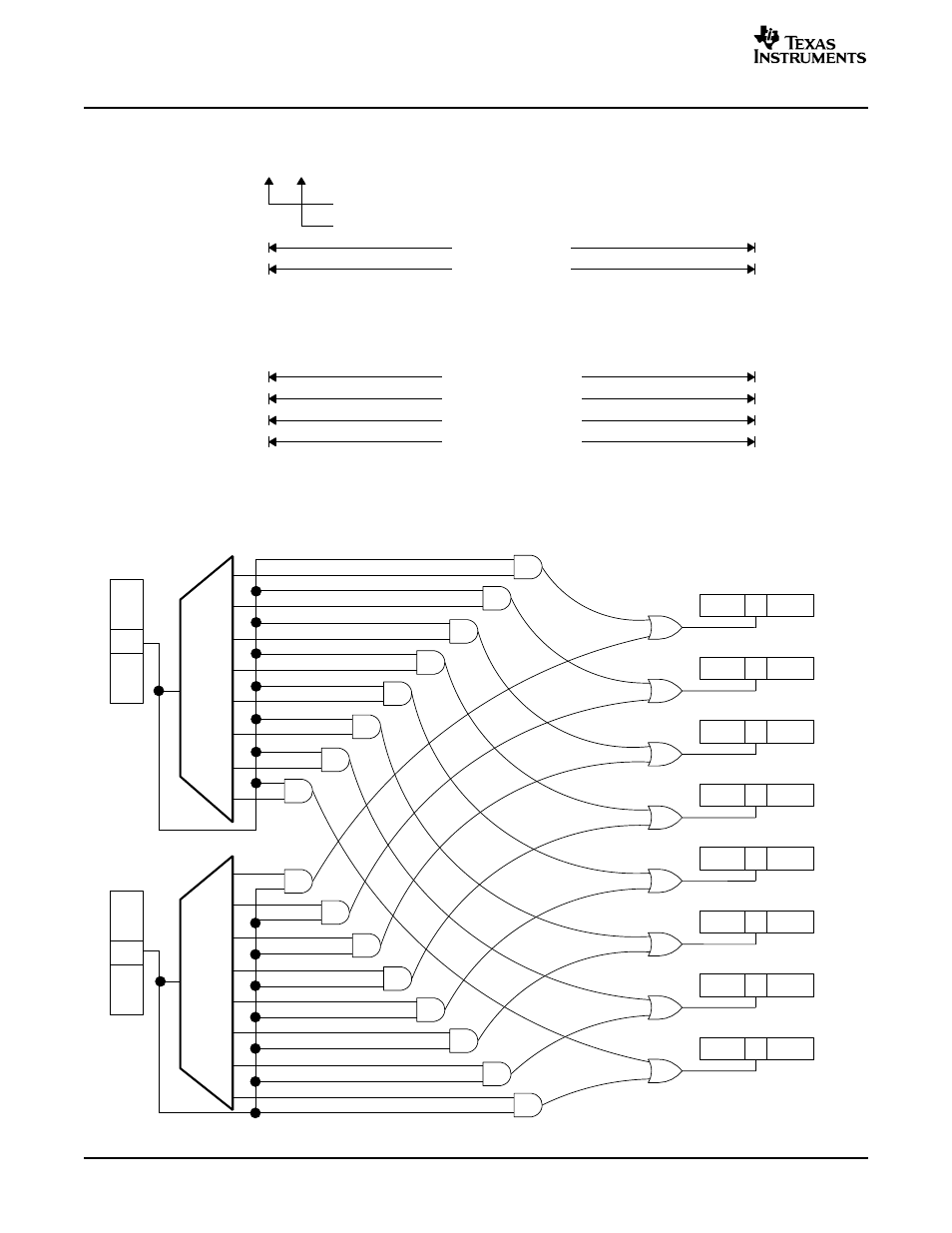

Interrupt Conditions

Figure 54. Sharing of ISDR Bits

As an example, if bit 29 of the ISDR is set, this indicates that there is a pending interrupt on either the TX

CPPI queue 2 or RX CPPI queue 2.

illustrates the decode routing.

Figure 55. Example Diagram of Interrupt Status Decode Register Mapping

84

Serial RapidIO (SRIO)

SPRU976 – March 2006