0x12c) – Texas Instruments TMS320C645X User Manual

Page 26

www.ti.com

SRIO Functional Description

2.3.2

SERDES and its Configurations

SRIO offers many benefits to customers by allowing a scalable non-proprietary interface. With the use of

TI’s SERDES macros, the peripheral is very adaptable and bandwidth scalable. The same peripheral can

be used for all three frequency nodes specified in V1.2 of the RapidIO specification (1.25, 2.5, and 3.125

Gbps). This allows you to design to only one protocol throughout the system and selectively choose the

bandwidth, thus eliminating the need for user’s proprietary protocols in many instances, and providing a

faster design turn and production ramp. Since this interface is serial, the application space is not limited to

a single board. It will propagate into backplane applications as well. Integration of these macros on an

ASIC or DSP allows you to reduce the number of discrete components on the board and eliminates the

need for bus driver chips.

Additionally, there are some valuable features built into TI SERDES. System optimization can be uniquely

managed to meet individual customer applications. For example, control registers within the SERDES

allow you to adjust the TX differential output voltage (Vod) on a per driver basis. This allows power

savings on short trace links (on the same board) by reducing the TX swing. Similarly, data edge rates can

be adjusted through the control registers to help reduce any EMI affects. Unused links can be individually

powered down without affecting the working links.

Because the high-speed analog nature of the SERDES is often the most critical portion of the RapidIO

peripheral, good test access is important.

The SERDES is a self-contained macro which includes transmitter (TX), receiver (RX), phase-locked-loop

(PLL), clock recovery, serial-to-parallel (S2P), and parallel-to-serial (P2S) blocks. The internal PLL

multiplies a user-supplied reference clock. All loop filter components of the PLL are onchip. Likewise, the

differential TX and RX buffers contain on-chip termination resistors. The only off-chip component

requirement is for DC blocking capacitors. These capacitors are needed only to ensure interoperability

between vendors and can be removed in cases where TI devices talk to other TI devices at the same

voltage node. The SERDES are designed for 1.2V

±

5% operation. This provides for excellent power

efficiency.

2.3.2.1

Enabling the PLL

The Physical layer SERDES has a built-in PLL, which is used for the clock recovery circuitry. The PLL is

responsible for clock multiplication of a slow speed reference clock. This reference clock has no timing

relationship to the serial data and is asynchronous to any CPU system clock. The multiplied high-speed

clock is only routed within the SERDES block, it is not distributed to the remaining blocks of the peripheral,

nor is it a boundary signal to the core of the device. It is extremely important to have a good quality

reference clock, and to isolate it and the PLL from all noise sources. A unique Reference Clock

Distribution (RCD) macro is used for this purpose. Since RapidIO requires 8b/10b encoded data, the 8-bit

mode of the SERDES PLL will not be used.

SERDES_CFGn_CNTL, SERDES_CFGRXn_CNTL, and SERDES_CFGTXn_CNTL registers are used to

configure SERDES. To enable the internal PLL, the ENPLL bit of SERDES_CFGn_CNTL must be set

high. After setting this bit, it is necessary to allow 1µs for the regulator to stabilize. Thereafter, the PLL will

take no longer than 200 reference clock cycles to lock to the required frequency, provided RIOCLK and

RIOCLK are stable.

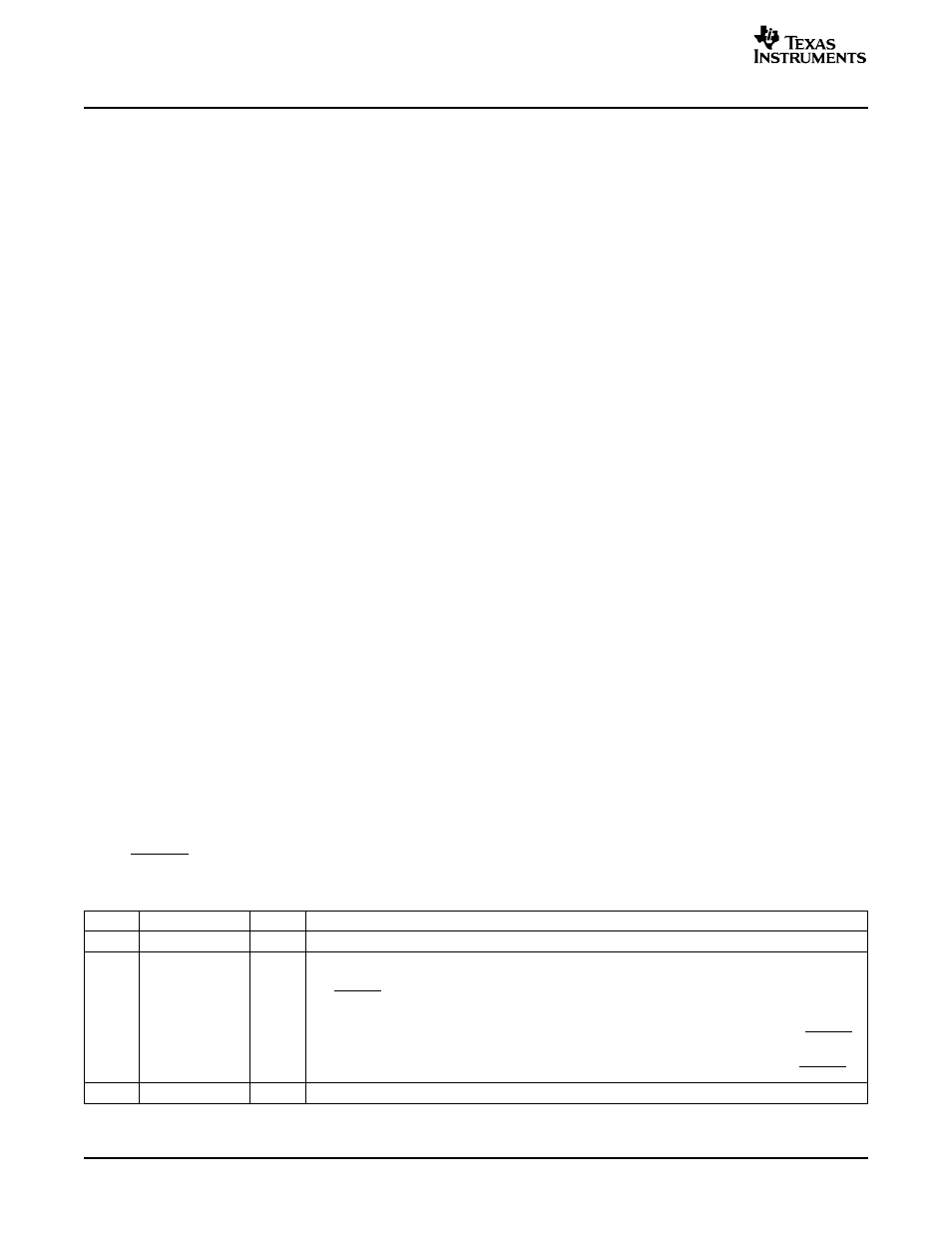

Table 4. Bits of SERDES_CFGn_CNTL Register (0x120 - 0x12c)

Bit

Name

Value

Description

31:10

Reserved

Reserved.

9:8

LB

Loop bandwidth. Specify loop bandwidth settings.

00

Frequency dependent bandwidth. The PLL bandwidth is set to a twelfth of the frequency of RIOCLK

and RIOCLK.

01

Reserved

10

Low bandwidth. The PLL bandwidth is set to a twentieth of the frequency of RIOCLK and RIOCLK,

or 3MHz (whichever is larger).

11

High bandwidth. The PLL bandwidth is set to an eighth of the frequency of RIOCLK and RIOCLK.

7:6

Reserved

Reserved.

26

Serial RapidIO (SRIO)

SPRU976 – March 2006