Cntl), Descriptions, Section 5.14 – Texas Instruments TMS320C645X User Manual

Page 114

www.ti.com

5.14

SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL)

SRIO Registers

There are four of these registers, to support four ports.

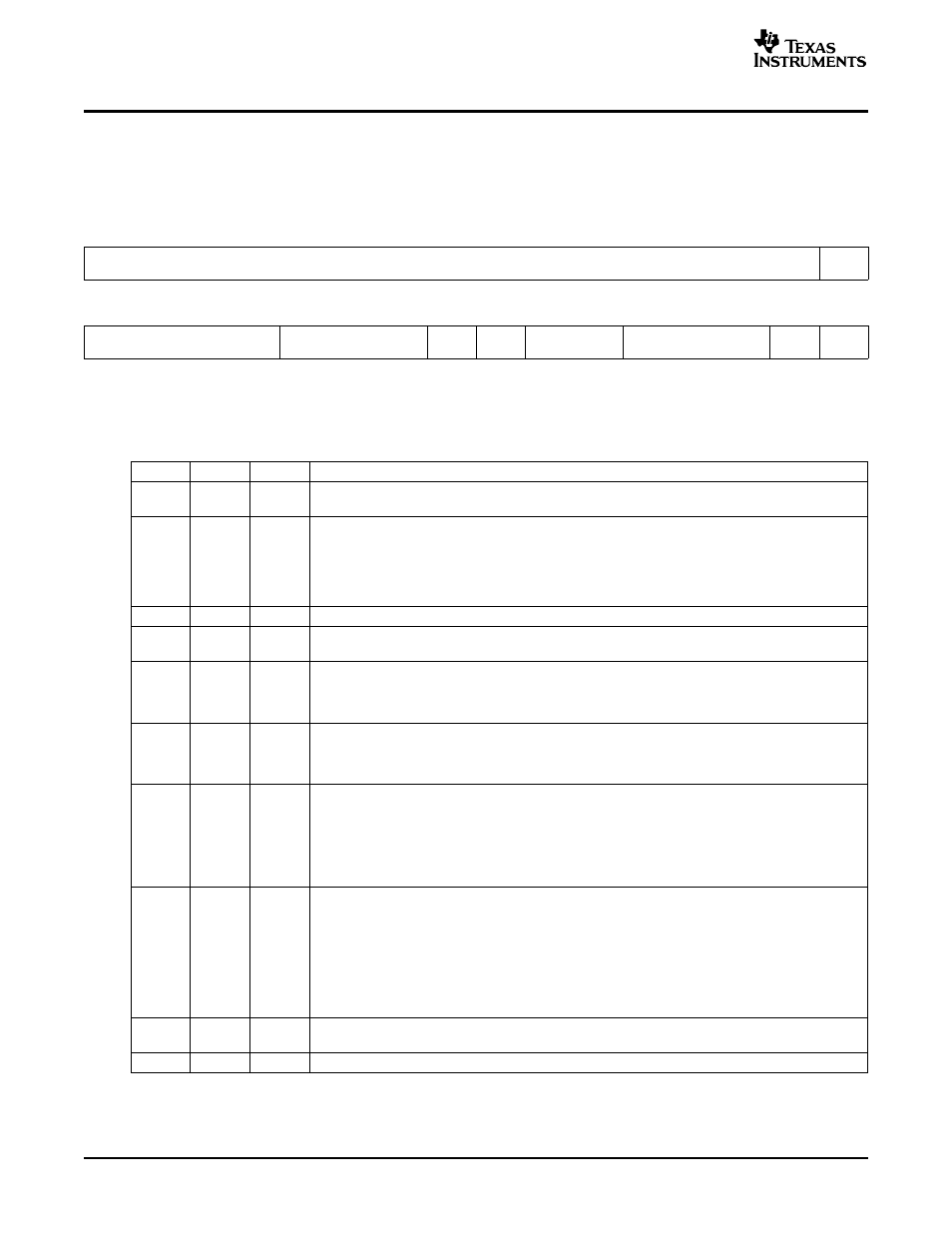

Figure 70. SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL)

31

17

16

Reserved

ENFT

P

R-0

R/W-0

15

12

11

9

8

7

6

5

4

2

1

0

DE

SWING

CM

INVPA

RATE

BUSWIDTH

Reserv

ENTX

IR

ed

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R = Read, W = Write, n = value at reset

Table 42. SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL) Field

Descriptions

Bit

Field

Value

Description

31:17

Reserve

Reserved.

d

16

ENFTP

Enable fixed TXBCKLINn phase. Enables fixed phase relationship of TXBCLKINn with respect to

TXBCLKn.

0

Arbitrary phase. No required phase relationship between TXBCLKINn and TXBCLKn.

1

Fixed phase. Requires direct connection of TXBCLKn to TXBCLKINn using a minimum length net

without buffers.

15:12

DE

De-emphasis. Selects one of 15 output de-emphasis settings from 4.76 to 71.42%. See

11:9

SWING

Output swing. Selects one of 8 outputs amplitude settings between 125 and 1250mV

dfpp

. See

8

CM

Common mode. Adjusts the common mode to suit the termination at the attached receiver.

0

Normal common mode. Common mode not adjusted.

1

Raised common mode. Common mode raised by 5% of e

54

.

7

INVPAIR

Invert polarity. Inverts polarity of TXPn and TXNn.

0

Normal polarity. TXPn considered to be positive data and TXNn negative.

1

Inverted polarity. TXPn considered to be negative data and TXNn positive.

6:5

RATE

Operating rate. Selects full, half or quarter rate operation.

00

Full rate. Two data samples taken per PLL output clock cycle.

01

Half rate. One data sample taken per PLL output clock cycle.

10

Quarter rate. One data sample taken every two PLL output clock cycles.

11

Reserved

4:2

BUS-

Bus width. Selects the width of the parallel interface (10 or 8 bit).

WIDTH

000

10-bit operation. Data is input on TDn[9:0]. TXBCLKn period is 10 bit periods (4 high, 6 low).

001

8-bit operation. Data is input on TDn[9:2]. TXBCLKn period is 8 bit periods (4 high, 4 low). TDn[1:0]

are ignored.

01x

Reserved

1xx

Reserved

1

Reserve

Reserved

d

0

ENTX

Enable transmitter. Enables this transmitter when high.

Serial RapidIO (SRIO)

114

SPRU976 – March 2006