Texas Instruments TMS320C645X User Manual

Page 25

www.ti.com

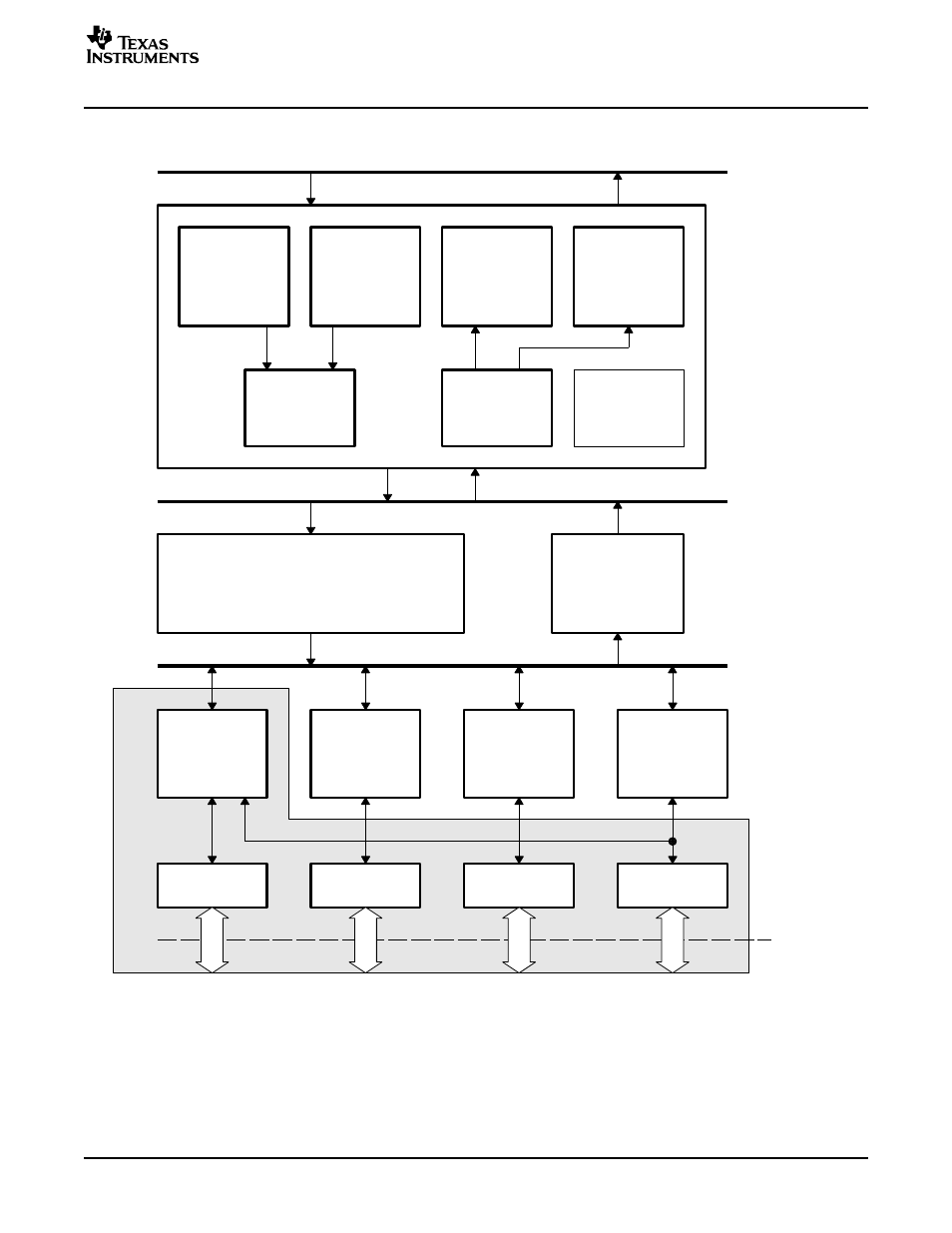

Port 0

8 x 276 TX

8 x 276 RX

8 x 276 RX

8 x 276 TX

Port 1

8 x 276 TX

8 x 276 RX

Port 2

8 x 276 RX

8 x 276 TX

Port 3

Physical

layer

buffers

SERDES 0

SERDES 1

SERDES 2

SERDES 3

SERDES

differential

signals

4x mode

data path

TX buffering

32 x 276B

8 buffers per 1X port - all priorities

32 buffers per 4X port - 8 per priority

Transaction

mapping

layer

buffers

Logical

Load/store

unit (LSU)

Tx direct I/O

Maintenance

Messaging

TXU

Rx direct I/O

(MAU)

Memory

access unit

RXU

Messaging

buffer

4.5 KB Tx

shared

buffer

shared

4.5 KB Tx

handle

Queue

128-bit

DMA bus 128-bit

SRIO Functional Description

Figure 8. SRIO Conceptual Block Diagram

SPRU976 – March 2006

Serial RapidIO (SRIO)

25