Transfers – Texas Instruments TMS320C645X User Manual

Page 77

www.ti.com

Interrupt Conditions

Where ICS0 - Doorbell1, bit 0, through ICS15 - Doorbell1, bit 15.

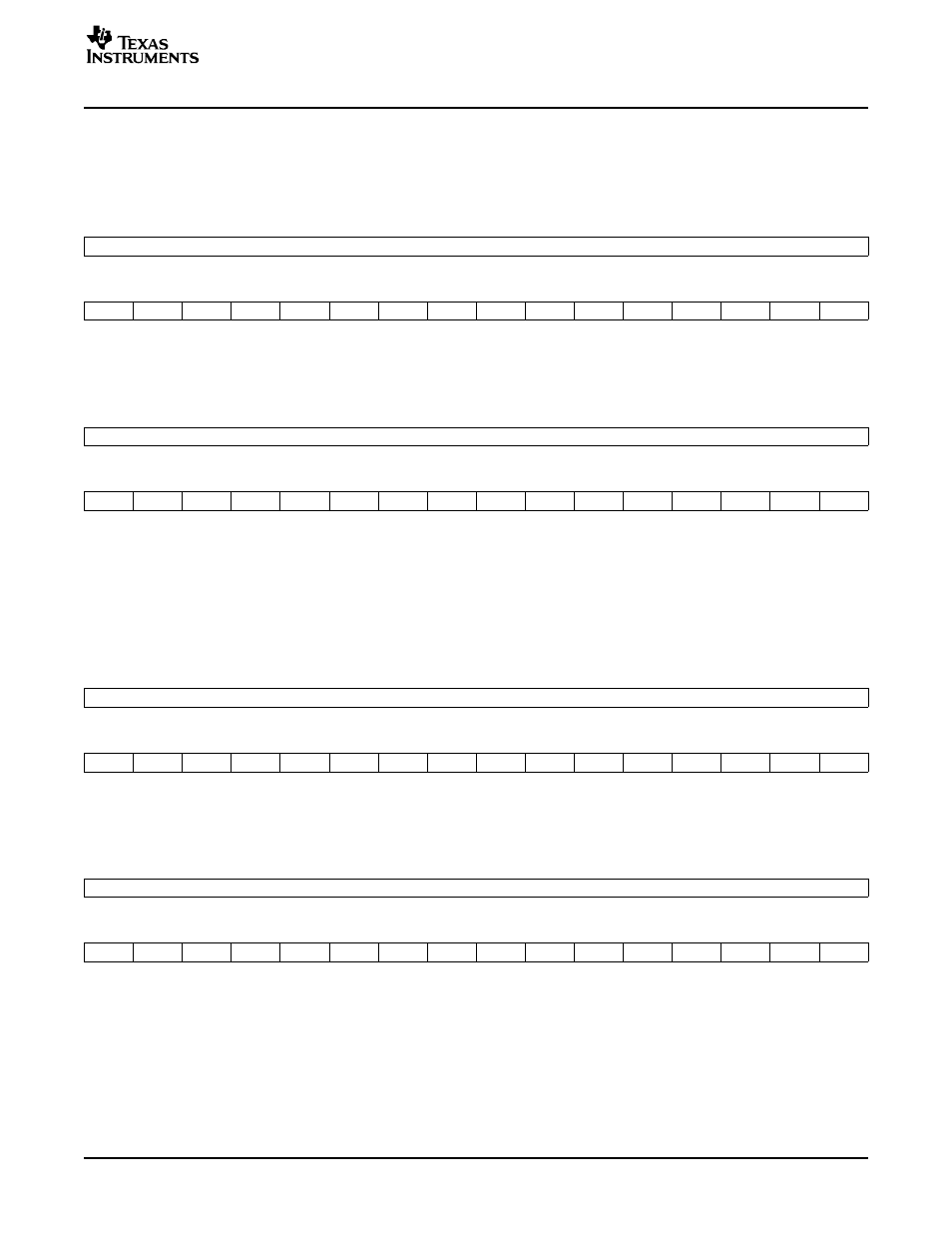

Figure 45. DOORBELL2 Interrupt Registers for Direct I/O Transfers

DOORBELL2 Interrupt Condition Status Registers (ICSR) (Address Offset 0x0220)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICS15

ICS14

ICS13

ICS12

ICS11

ICS10

ICS9

ICS8

ICS7

ICS6

ICS5

ICS4

ICS3

ICS2

ICS1

ICS0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R = Read, W = Write, n = value at reset

DOORBELL2 Interrupt Condition Clear Registers (ICCR) (Address Offset 0x0228)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICC15

ICC14

ICC13

ICC12

ICC11

ICC10

ICC9

ICC8

ICC7

ICC6

ICC5

ICC4

ICC3

ICC2

ICC1

ICC0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

LEGEND: R = Read, W = Write, n = value at reset

Where ICS0 - Doorbell2, bit 0, through ICS15 - Doorbell2, bit 15.

Figure 46. DOORBELL3 Interrupt Registers for Direct I/O Transfers

DOORBELL3 Interrupt Condition Status Registers (ICSR) (Address Offset 0x0230)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICS15

ICS14

ICS13

ICS12

ICS11

ICS10

ICS9

ICS8

ICS7

ICS6

ICS5

ICS4

ICS3

ICS2

ICS1

ICS0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R = Read, W = Write, n = value at reset

DOORBELL3 Interrupt Condition Clear Registers (ICCR) (Address Offset 0x0238)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICC15

ICC14

ICC13

ICC12

ICC11

ICC10

ICC9

ICC8

ICC7

ICC6

ICC5

ICC4

ICC3

ICC2

ICC1

ICC0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

W-0

LEGEND: R = Read, W = Write, n = value at reset

Where ICS0 - Doorbell3, bit 0, through ICS15 - Doorbell3, bit 15.

SPRU976 – March 2006

Serial RapidIO (SRIO)

77