Texas Instruments TMS320C645X User Manual

Page 51

www.ti.com

SRIO Functional Description

Table 20. TX Buffer Descriptor Field Definitions (continued)

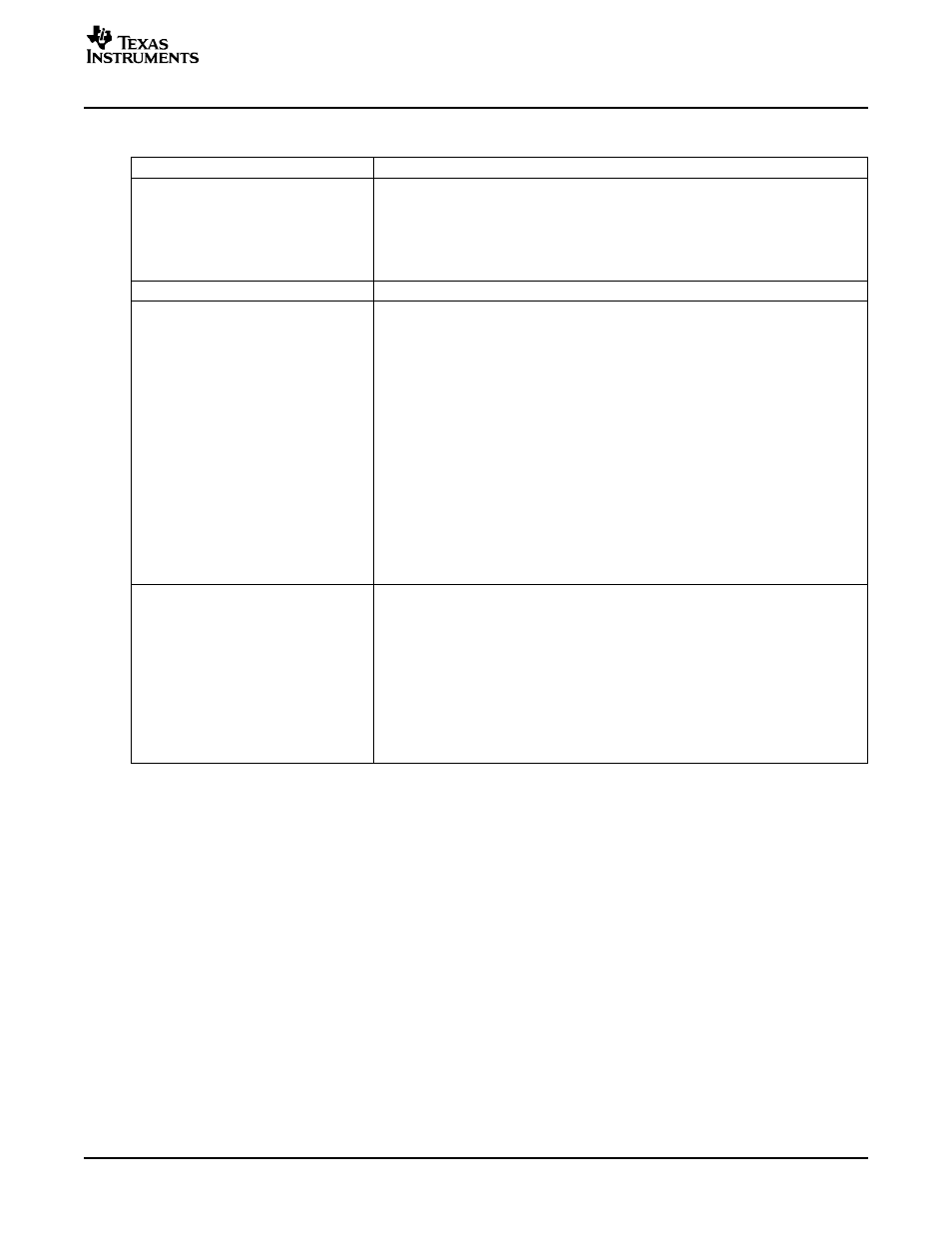

Field

Description

tt

RapidIO tt field specifying 8- or 16-bit DeviceIDs

00: 8b deviceIDs

01: 16b deviceIDs

10: reserved

11: reserved

PortID

Port number for routing outgoing packet.

SSIZE

RIO standard message payload size. Indicates how the hardware should segment the

outgoing message by specifying the maximum number of double-words per packet. If

the message is a multi-segment message, this field remains the same for all outgoing

segments. All segments of the message, except for the last segment, have payloads

equal to this size. The last message segment may be equal or less than this size.

Maximum message size for a 16 segment message is shown below.

Message_length/16 must be less than or equal to Ssize, if not, the message is not sent

and CC 101b is set.

0000b - 1000b: Reserved

1001b: 1 Double-word payload (Supports up to a 128B message)

1010b: 2 Double-word payload (Supports up to a 256B message)

1011b: 4 Double-word payload (Supports up to a 512B message)

1100b: 8 Double-word payload (Supports up to a 1024B message)

1101b: 16 Double-word payload (Supports up to a 2048B message)

1110b: 32 Double-word payload (Supports up to a 4096B message)

1111b: Reserved

mailbox

Destination Mailbox: Specifies the mailbox to which the message will be sent.

000000b: Mailbox 0

000001b: Mailbox 1

. . .

000100b: Mailbox 4

. . .

111111b: Mailbox 63

For multi-segment messages, only the 2 LSBs of this mailbox field are valid. Hardware

will ignore the 4 MSBs of this field if the outgoing message is multi-segment.

Once the port controls the buffer descriptor, the DEST_ID field can be queried to determine flow control. If

the transaction has been flow controlled, the DMA bus READ request is postponed so that the TX buffer

space is not wasted. Because buffer descriptors cannot be reordered in the link list, if the transaction at

the head of the buffer descriptor queue is flow controlled, HOL blocking will occur on that queue. When

this occurs, all transactions located in that queue are stalled. To counter the affects and reduce back-up of

more TX packets, multiple queues are available. The peripheral supports a total of 16 assignable TX

queues and their associated TX DMA state registers. The transmission order between queues is based on

programmable weighted round-robin at the message level. The programmable registers are shown in

. This scheme allows configurability of the queue transmission order, as well as the weight of

each queue within the round robin. Upon enabling the peripheral with the Peripheral Control Register

(0x0004), the TX state machine begins by processing the TX_Queue_Map0. It will attempt to process the

queue and number of buffer descriptors from that queue programmed in this mapper. Then it will move to

TX_Queue_Map1, followed by TX_Queue_Map2 and so forth. It is important to note that this mapping

order is fixed in a circular pattern. Each mapper can point to any queue and multiple mappers can point to

a single queue. If a mapper points to an in-active queue, the peripheral recognizes this and moves to the

next mapper. In order for an active queue to transmit packets, at least one mapper must be pointing to

that queue. The default settings dictate an equally weighted round robin that starts on queue0 and

increments by one until reaching queue15. If the application requires precise control over the order of data

sent out of the device after power up or reset, you should program the map control registers, set up the

TX queues and initialize the HDP, and finally enable the peripheral with the Peripheral Control Register.

SPRU976 – March 2006

Serial RapidIO (SRIO)

51