Srio functional description – Texas Instruments TMS320C645X User Manual

Page 62

www.ti.com

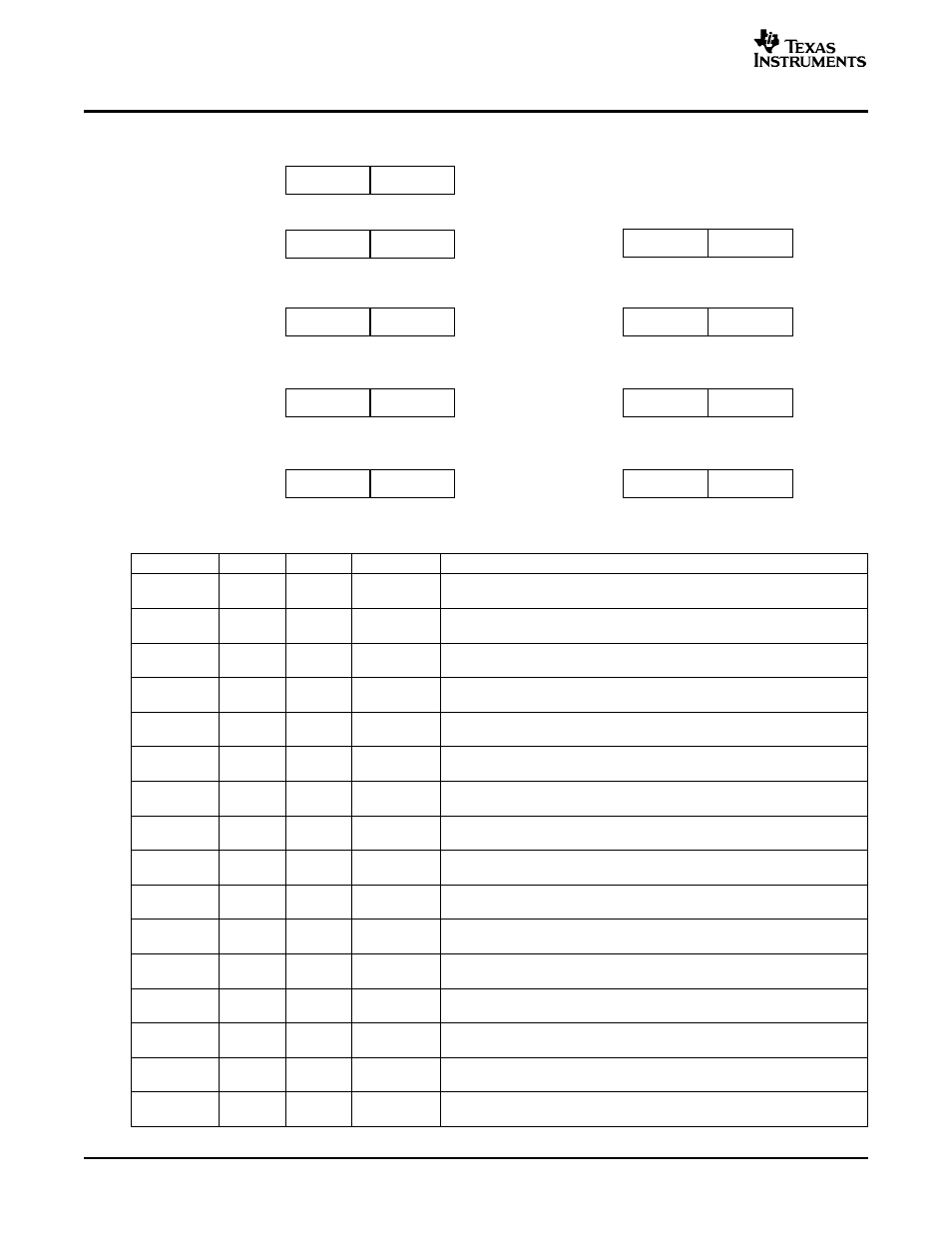

Reserved

RIO_LSUn_FLOW_MASKS

(Address Offsets: 0x041C,

0x043C, 0x045C, 0x047C)

31-16

R, 0x0000

LSU n Flow Mask

15-0

R/W, 0xFFFF

TX Queue1

Flow Mask

RIO_TX_CPPI_FLOW_MASKS0

(Address Offsets: 0x0704)

31-16

R/W, 0xFFFF

TX Queue0

Flow Mask

15-0

R/W, 0xFFFF

TX Queue3

Flow Mask

RIO_TX_CPPI_FLOW_MASKS1

(Address Offsets: 0x0708)

31-16

R/W, 0xFFFF

TX Queue2

Flow Mask

15-0

R/W, 0xFFFF

TX Queue5

Flow Mask

RIO_TX_CPPI_FLOW_MASKS2

(Address Offsets: 0x070C)

31-16

R/W, 0xFFFF

TX Queue4

Flow Mask

15-0

R/W, 0xFFFF

TX Queue7

Flow Mask

RIO_TX_CPPI_FLOW_MASKS3

(Address Offsets: 0x0710)

31-16

R/W, 0xFFFF

TX Queue6

Flow Mask

15-0

R/W, 0xFFFF

TX Queue9

Flow Mask

RIO_TX_CPPI_FLOW_MASKS4

(Address Offsets: 0x0714)

31-16

R/W, 0xFFFF

TX Queue8

Flow Mask

15-0

R/W, 0xFFFF

TX Queue11

Flow Mask

RIO_TX_CPPI_FLOW_MASKS5

(Address Offsets: 0x0718)

31-16

R/W, 0xFFFF

TX Queue10

Flow Mask

15-0

R/W, 0xFFFF

TX Queue13

Flow Mask

RIO_TX_CPPI_FLOW_MASKS6

(Address Offsets: 0x071C)

31-16

R/W, 0xFFFF

TX Queue12

Flow Mask

15-0

R/W, 0xFFFF

TX Queue15

Flow Mask

RIO_TX_CPPI_FLOW_MASKS7

(Address Offsets: 0x0720)

31-16

R/W, 0xFFFF

TX Queue14

Flow Mask

15-0

R/W, 0xFFFF

SRIO Functional Description

Figure 28. Transmit Source Flow Control Masks

Table 23. Transmit Source Flow Control Masks

Name

Bit

Access

Reset Value

Description

Flow Mask

0

R/W

1b

0b – TX source doesn’t support Flow0 from table entry

1b – TX source does support Flow0 from table entry

Flow Mask

1

R/W

1b

0b – TX source doesn’t support Flow1 from table entry

1b – TX source does support Flow1 from table entry

Flow Mask

2

R/W

1b

0b – TX source doesn’t support Flow2 from table entry

1b – TX source does support Flow2 from table entry

Flow Mask

3

R/W

1b

0b – TX source doesn’t support Flow3 from table entry

1b – TX source does support Flow3 from table entry

Flow Mask

4

R/W

1b

0b – TX source doesn’t support Flow4 from table entry

1b – TX source does support Flow4 from table entry

Flow Mask

5

R/W

1b

0b – TX source doesn’t support Flow5 from table entry

1b – TX source does support Flow5 from table entry

Flow Mask

6

R/W

1b

0b – TX source doesn’t support Flow6 from table entry

1b – TX source does support Flow6 from table entry

Flow Mask

7

R/W

1b

0b – TX source doesn’t support Flow7 from table entry

1b – TX source does support Flow7 from table entry

Flow Mask

8

R/W

1b

0b – TX source doesn’t support Flow8 from table entry

1b – TX source does support Flow8 from table entry

Flow Mask

9

R/W

1b

0b – TX source doesn’t support Flow9 from table entry

1b – TX source does support Flow9 from table entry

Flow Mask

10

R/W

1b

0b – TX source doesn’t support Flow10 from table entry

1b – TX source does support Flow10 from table entry

Flow Mask

11

R/W

1b

0b – TX source doesn’t support Flow11 from table entry

1b – TX source does support Flow11 from table entry

Flow Mask

12

R/W

1b

0b – TX source doesn’t support Flow12 from table entry

1b – TX source does support Flow12 from table entry

Flow Mask

13

R/W

1b

0b – TX source doesn’t support Flow13 from table entry

1b – TX source does support Flow13 from table entry

Flow Mask

14

R/W

1b

0b – TX source doesn’t support Flow14 from table entry

1b – TX source does support Flow14 from table entry

Flow Mask

15

R/W

1b

0b – TX source doesn’t support Flow15 from table entry

1b – TX source does support Flow15 from table entry

Serial RapidIO (SRIO)

62

SPRU976 – March 2006