Texas Instruments TMS320C645X User Manual

Page 31

www.ti.com

SRIO Functional Description

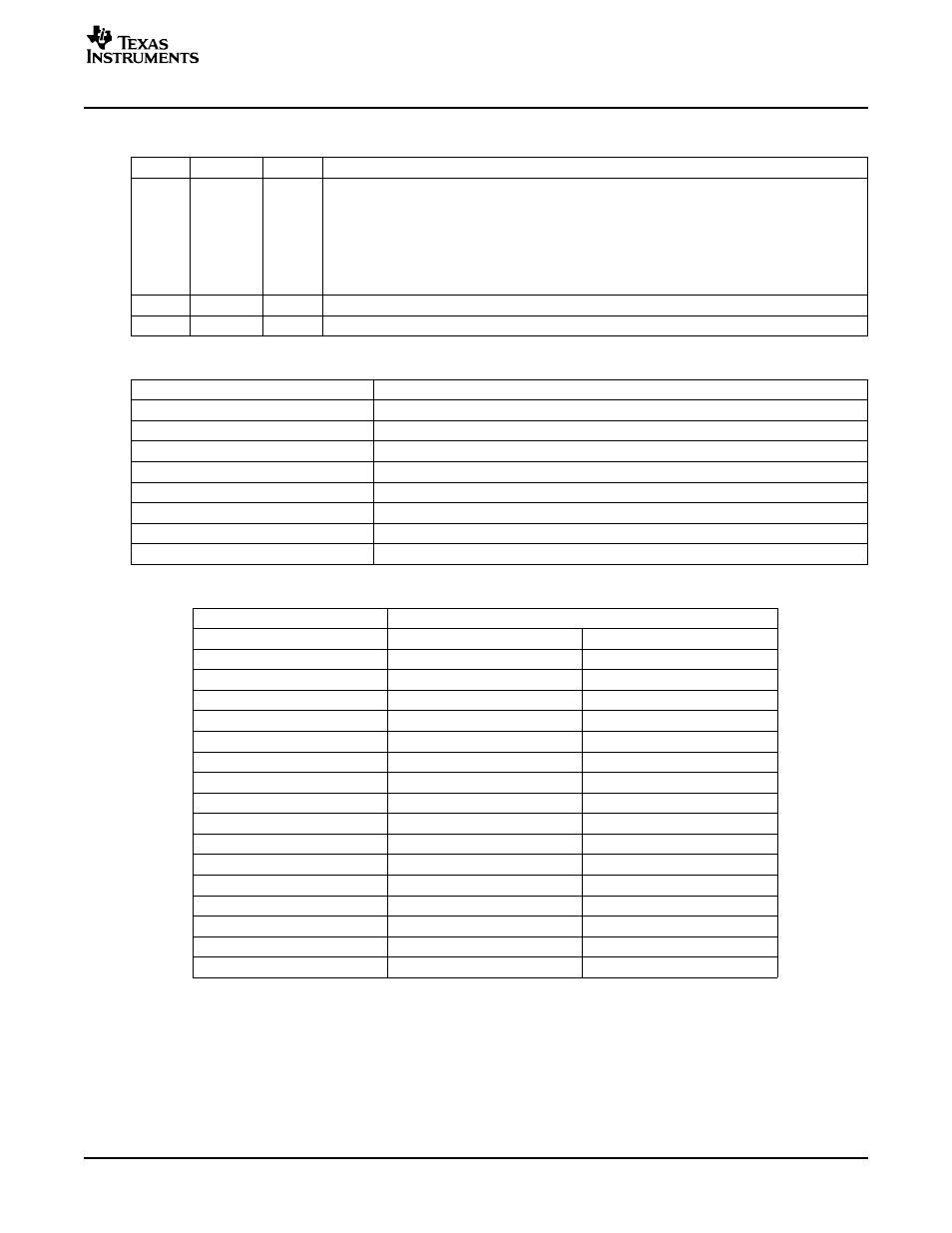

Table 10. Bits of SERDES_CFGTXn_CNTL Registers (continued)

Bit

Field

Value

Description

4:2

BUS-

Bus width. Selects the width of the parallel interface (10 or 8 bit).

WIDTH

000

10-bit operation. Data is input on TDn[9:0]. TXBCLKn period is 10 bit periods (4 high, 6 low).

001

8-bit operation. Data is input on TDn[9:2]. TXBCLKn period is 8 bit periods (4 high, 4 low).

TDn[1:0] are ignored.

01x

Reserved

1xx

Reserved

1

Reserved

Reserved

0

ENTX

Enable transmitter. Enables this transmitter when high.

Table 11. SWING Bits

CFGTX[11:9]

Amplitude (mV

dfpp

)

000

125

001

250

010

500

011

625

100

750

101

1000

110

1125

111

1250

Table 12. DE Bits

CFGTX[15:12]

Amplitude Reduction

%

dB

0000

0

0

0001

4.76

-0.42

0010

9.52

-0.87

0011

14.28

-1.34

0100

19.04

-1.83

0101

23.8

-2.36

0110

28.56

-2.92

0111

33.32

-3.52

1000

38.08

-4.16

1001

42.85

-4.86

1010

47.61

-5.61

1011

52.38

-6.44

1100

57.14

-7.35

1101

61.9

-8.38

1110

66.66

-9.54

1111

71.42

-10.87

SPRU976 – March 2006

Serial RapidIO (SRIO)

31