Texas Instruments TMS320C645X User Manual

Page 27

www.ti.com

SRIO Functional Description

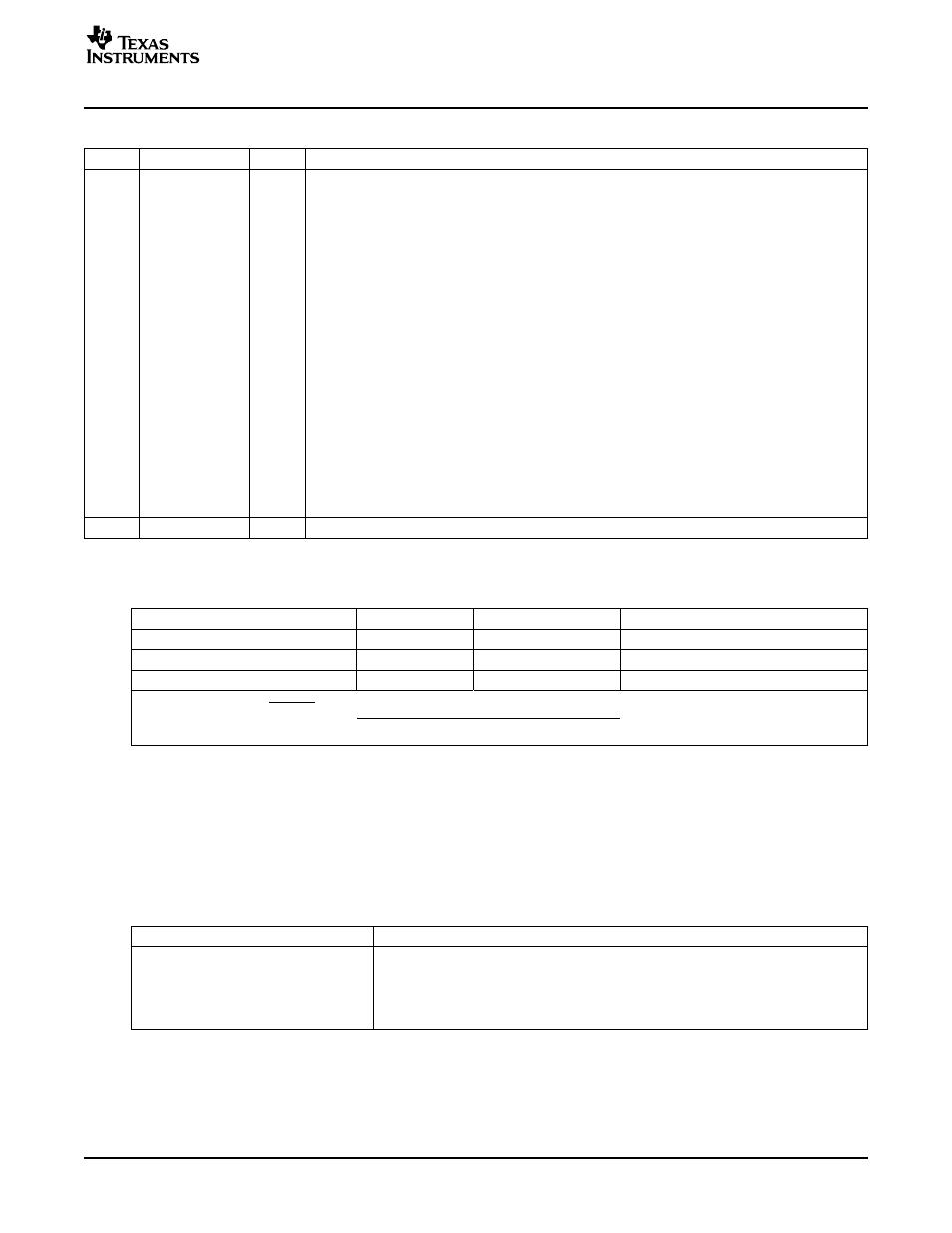

Table 4. Bits of SERDES_CFGn_CNTL Register (0x120 - 0x12c) (continued)

Bit

Name

Value

Description

5:1

MPY

PLL multiply. Select PLL multiply factors between 4 and 60. Multiply modes shown below.

0000

4x

0001

5x

0010

6x

0011

Reserved

0100

8x

0101

10x

0110

12x

0111

12.5x

1000

15x

1001

20x

1010

25x

1011

Reserved

1100

Reserved

1101

50x

1110

60x

1111

Reserved

0

ENPLL

Enable PLL. Enables the PLL.

Based on the MPY value, the following line rate versus PLL output clock frequency can be estimated:

Table 5. Line Rate versus PLL Output Clock Frequency

Rate

Line Rate

PLL Output Frequency

RATESCALE

Full

x Gbps

0.5x GHz

0.5

Half

x Gbps

x GHz

1

Quarter

x Gbps

2x GHz

2

RIOCLK and RIOCLK

FREQ

=

LINERATE

×

RATESCALE

MPY

The rate is defined by the RATE bits of the SERDES_CFGRXn_CNTL register and the

SERDES_CFGTXn_CNTL register, respectively.

The primary operating frequency of the SERDES macro is determined by the reference clock frequency

and PLL multiplication factor. However, to support lower frequency applications, each receiver and

transmitter can also be configured to operate at a half or quarter of this rate via the RATE bits of the

SERDES_CFGRXn_CNTL and SERDES_CFGTXn_CNTL registers as described in

Table 6. RATE Bit Effects

Value

Description

0 0

Full rate. Two data samples taken per PLL output clock cycle.

0 1

Half rate. One data sample taken per PLL output clock cycle.

1 0

Quarter rate. One data sample taken every two PLL output clock cycles.

1 1

Reserved.

SPRU976 – March 2006

Serial RapidIO (SRIO)

27