0x0030), 0x0038) – Texas Instruments TMS320C645X User Manual

Page 65

www.ti.com

SRIO Functional Description

2.3.9.1

Reset Summary

After reset, the state of the peripheral depends on the default register values and the BLKn_EN_INIT tieoff

values.

You can also perform a hard reset using the software of each logical block within the peripheral via the

GBL_EN and BLKn_EN bits. The GBL_EN bits reset the peripheral, while the rest of the device is not

reset. The BLKn_EN bits shut down unused portions of the peripheral. The *EN functionality will minimize

power by resetting the appropriate logical block(s), and gating off the clock to the appropriate logical

block(s). This should be considered an abrupt reset independent of the state of the peripheral, and should

be capable of resetting the peripheral to its original state.

Upon reset of the peripheral, the device must reestablish communication with its link partner. Depending

on the system, this may include a discovery phase in which a host processor reads the peripheral’s

CAR/CSR registers to determine its capabilities. In its simplest form, it involves retraining the SERDES

and going through the initialization phase to synchronize on bit and word boundaries by using idle and

control symbols, as described in section 5.5.2 of the Part VI of the RapidIO specification. Until the

peripheral and its partner are fully initialized and ready for normal operation, the peripheral will not send

any data packets or non-status control symbols.

•

GBL_EN_INIT and BLK_EN_INIT[n:0]: These module boundary signals are static tieoffs which control

the default state of the GBL_EN and BLK_EN[n:0] MMRs.

•

GBL_EN: Resets all MMRs, excluding Reset Ctl Values (0x0000 – 0x1FC). Resets all logical blocks

except MMR configuration bus i/f. While asserted, the slave configuration bus is operational.

•

BLK_EN0: Resets all MMRs, excluding Reset Ctl Values (0x0000 – 0x1FC). Other logical blocks are

unaffected, including MMR configuration bus i/f.

•

BLK_EN[n:1]: Single enable/reset per logical block.

2.3.9.2

Enable and Enable Status Registers

through

are the register diagrams for the enable and enable status registers.

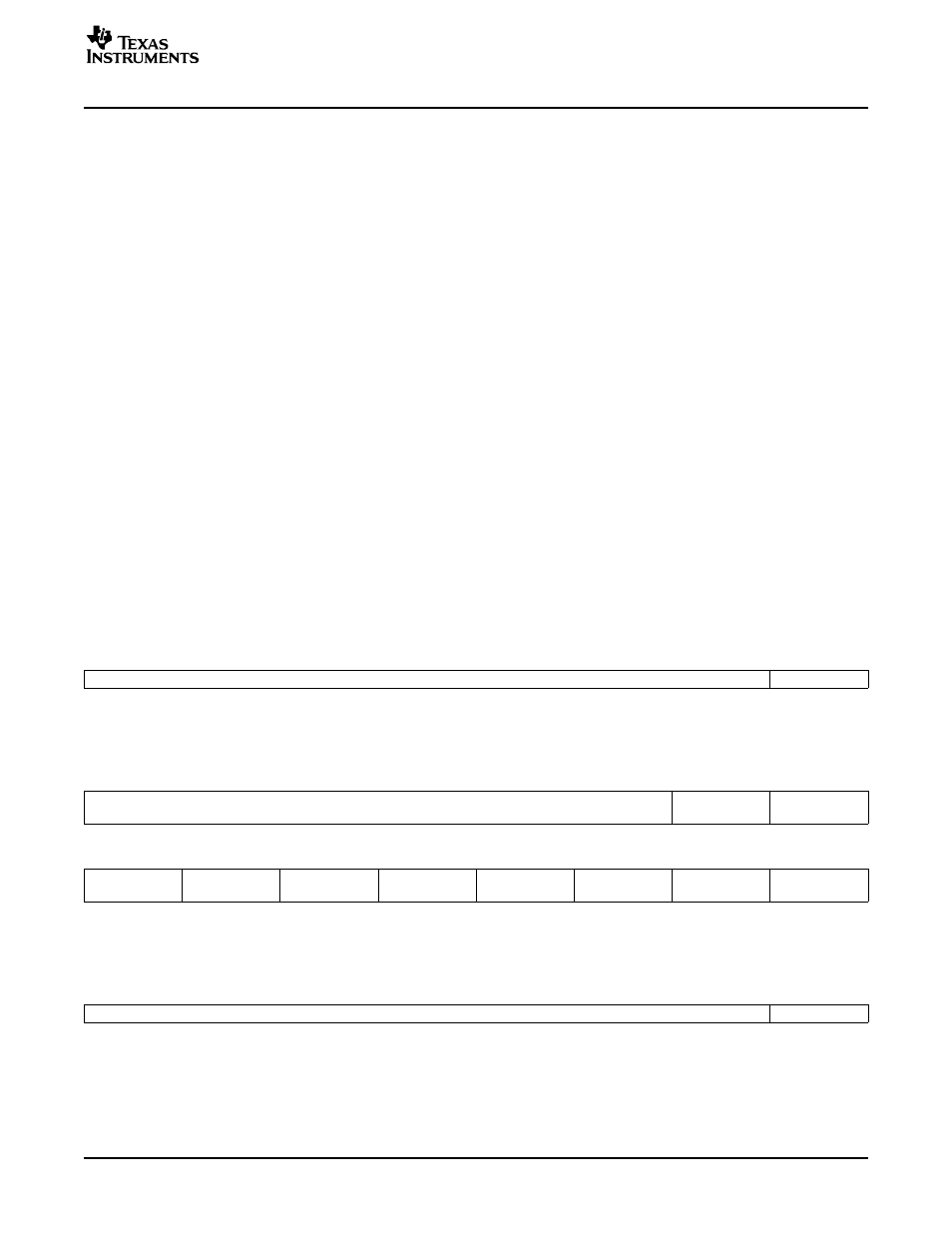

Figure 31. GBL_EN (Address 0x0030)

31

1

0

Reserved

EN

R-0

R/W-1

LEGEND: R = Read, W = Write, n = value at reset

Figure 32. GBL_EN_STAT (Address 0x0034)

15

10

9

8

Reserved

BLK8_EN_STA

BLK7_EN_STA

T

T

R-0

R-1

R-1

7

6

5

4

3

2

1

0

BLK6_EN_STA

BLK5_EN_STA

BLK4_EN_STA

BLK3_EN_STA

BLK2_EN_STA

BLK1_EN_STA

BLK0_EN_STA GBL_EN_STAT

T

T

T

T

T

T

T

R-1

R-1

R-1

R-1

R-1

R-1

R-1

R-1

LEGEND: R = Read, W = Write, n = value at reset

Figure 33. BLK0_EN (Address 0x0038)

31

1

0

Reserved

EN

R-0

R/W-1

LEGEND: R = Read, W = Write, n = value at reset

SPRU976 – March 2006

Serial RapidIO (SRIO)

65