Per_set_cntl), Descriptions, Section 5.4 – Texas Instruments TMS320C645X User Manual

Page 101

www.ti.com

5.4

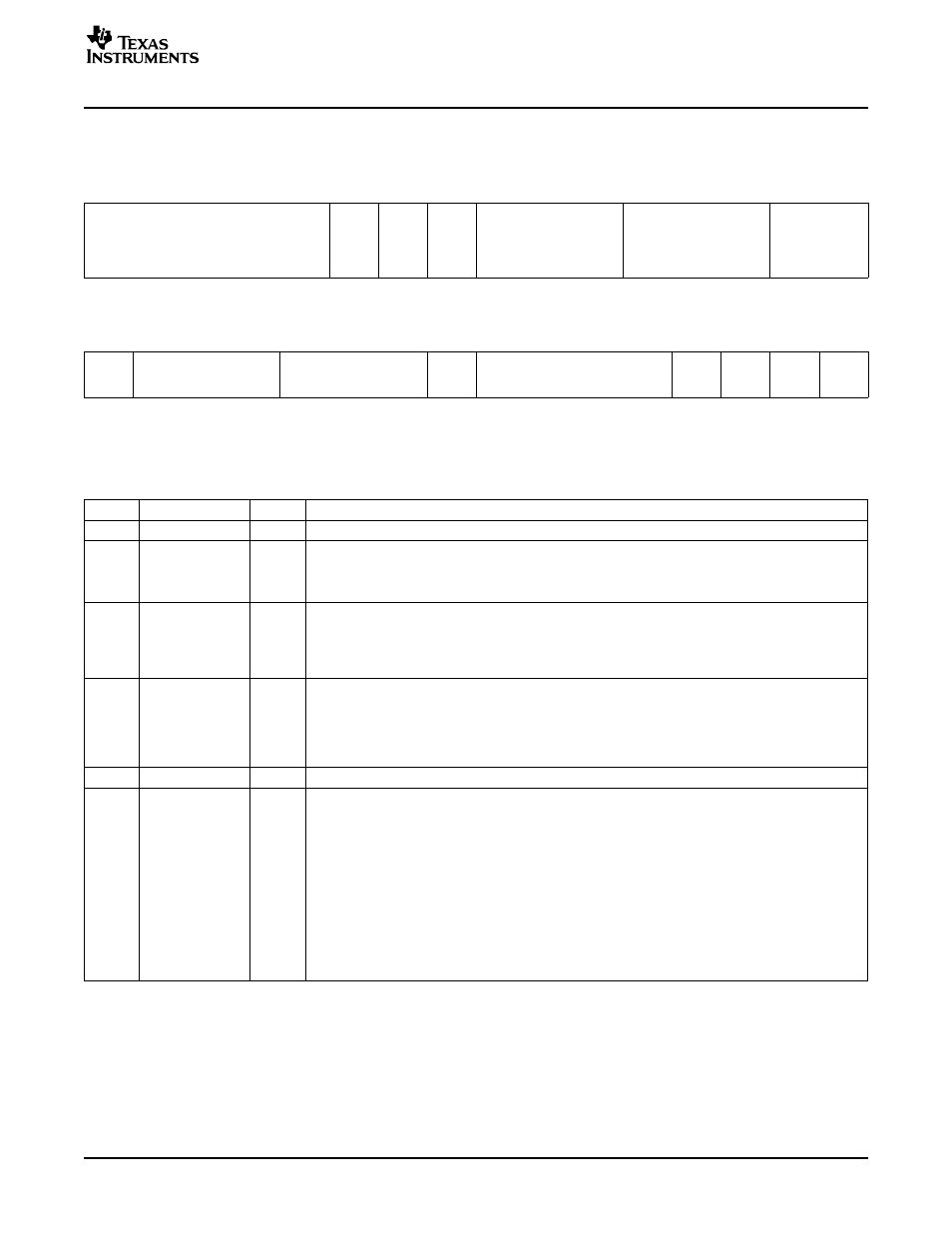

Peripheral Settings Control Register (PER_SET_CNTL)

SRIO Registers

Figure 60. Peripheral Settings Control Register (PER_SET_CNTL)

31-27

26

25

24

23-21

20-18

17-16

Reserved

SW_M

LOOP

BOOT

Reserved

TX_PRI2_WM

TX_PRI1_WM

EM_S

BACK

_COM

LEEP_

PLETE

OVER

RIDE

R-0x00

RW-

RW-

RW-

R-0x00

RW-0x01

RW-0x02

0x01

0x00

0x00

LEGEND: R = Read only; -n = value after reset

15

14-12

11-9

8

7-4

3

2

1

0

TX_P

TX_PRI0_WM

CBA_TRANS_PRI

1X_M

PRESCALER_SELECT

ENPLL ENPLL ENPLL ENPLL

RI1_W

ODE

4

3

2

1

M

RW-

RW-0x03

RW-0x00

RW-

RW-0x0000

RW-

RW-

RW-

RW-

0x02

0x00

0x00

0x00

0x00

0x00

LEGEND: R = Read only; -n = value after reset

Table 31. Peripheral Settings Control Register (PER_SET_CNTL) Field Descriptions

Bit

Field

Value

Description

31-27

Reserved

Reserved

26

SW_MEM_SLEE

Software Memory Sleep Override

P_OVERRIDE

0b

Memories are put in sleep mode while in shutdown

1b

Memories are not put in sleep mode while in shutdown

25

LOOPBACK

Loopback mode.

0b

Normal operation

1b

Loop back mode. Transmit data to receive on the same port. Packet data is looped back in the

digital domain before the SERDES macros.

24

BOOT_COMPLE

Controls ability to write any register during initialization. It also includes read only registers during

TE

normal mode of operation that have application defined reset value.

0b

Write to read only registers enabled

1b

Write to read only registers disabled. Usually the boot_complete is asserted once after reset to

define power on configuration.

23-21

Reserved

Reserved

20-18

TX_PRI2_WM

Transmit credit threshold. Sets the required number of logical layer TX buffers needed to send

priority 2 packets across the UDI interface. This is valid for all ports in 1X mode only.

Required buffer count for transmit credit threshold 2 value (TX_PRI2_WM):

•

000

→

8, 7, 6, 5, 4, 3, 2, 1

•

001

→

8, 7, 6, 5, 4, 3, 2

•

010

→

8, 7, 6, 5, 4, 3

•

011

→

8, 7, 6, 5, 4

•

100

→

8, 7, 6, 5

•

101

→

8, 7, 6

•

110

→

8, 7

•

111

→

8

SPRU976 – March 2006

Serial RapidIO (SRIO)

101