Icrr2), Descriptions, Section 5.27 – Texas Instruments TMS320C645X User Manual

Page 128

www.ti.com

5.27

DOORBELLn Interrupt Condition Routing Register 2 (DOORBELLn_ICRR2)

SRIO Registers

Each of the four doorbells is supported by a register of this type.

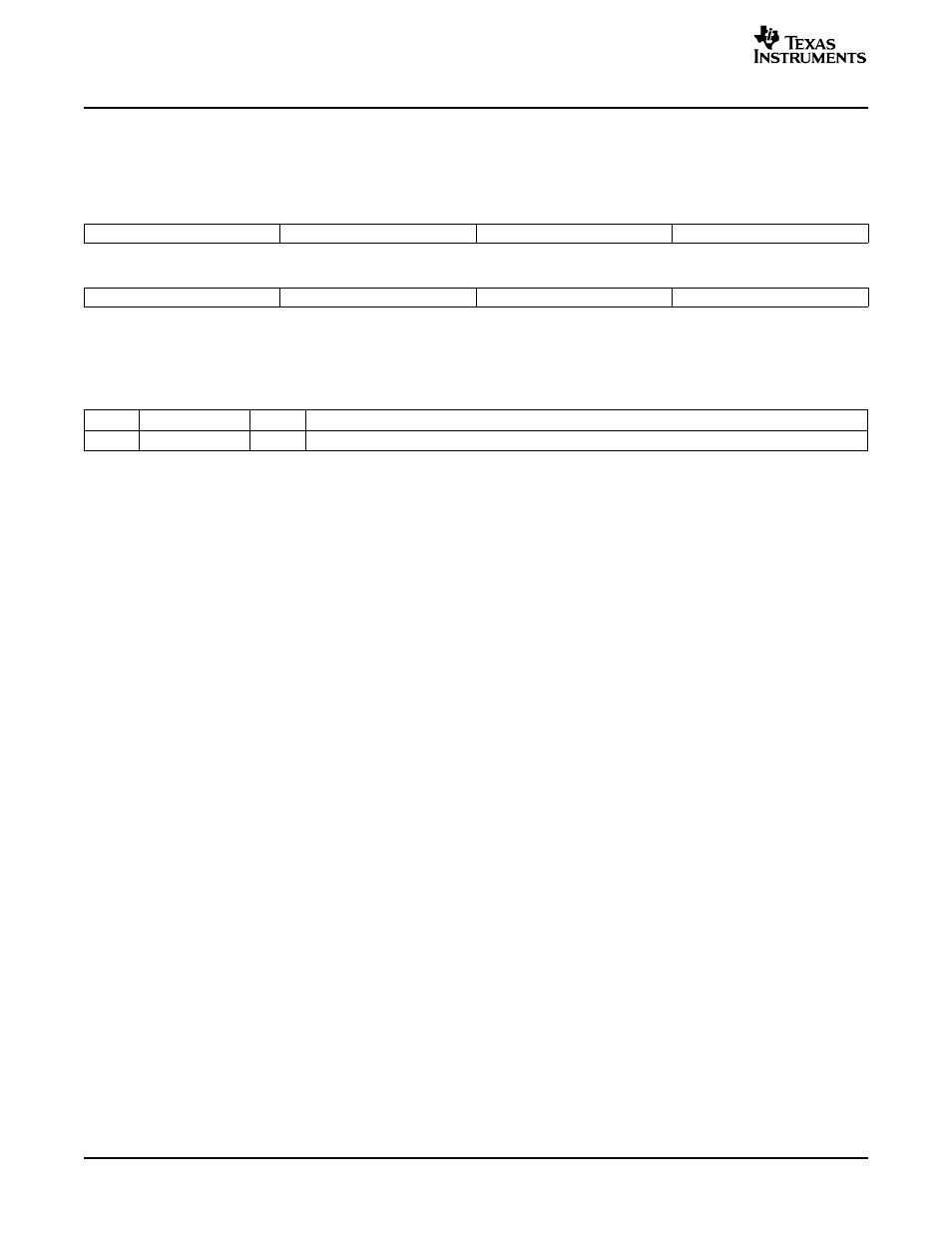

Figure 83. DOORBELLn Interrupt Condition Routing Register 2 (DOORBELLn_ICRR2)

31

28

27

24

23

20

19

16

ICR15

ICR14

ICR13

ICR12

R/W-0x00

R/W-0x00

R/W-0x00

R/W-0x00

15

12

11

8

7

4

3

0

ICR11

ICR10

ICR9

ICR8

R/W-0x00

R/W-0x00

R/W-0x00

R/W-0x00

LEGEND: R = Read, W = Write, n = value at reset

Table 57. DOORBELLn Interrupt Condition Routing Register 2 (DOORBELLn_ICRR2) Field

Descriptions

Bit

Field

Value

Description

31-0

ICR (8-15)

Doorbell n (0 to 3) CPU servicing interrupt condition routing bits

Serial RapidIO (SRIO)

128

SPRU976 – March 2006