Figure 27 – Texas Instruments TMS320C645X User Manual

Page 61

www.ti.com

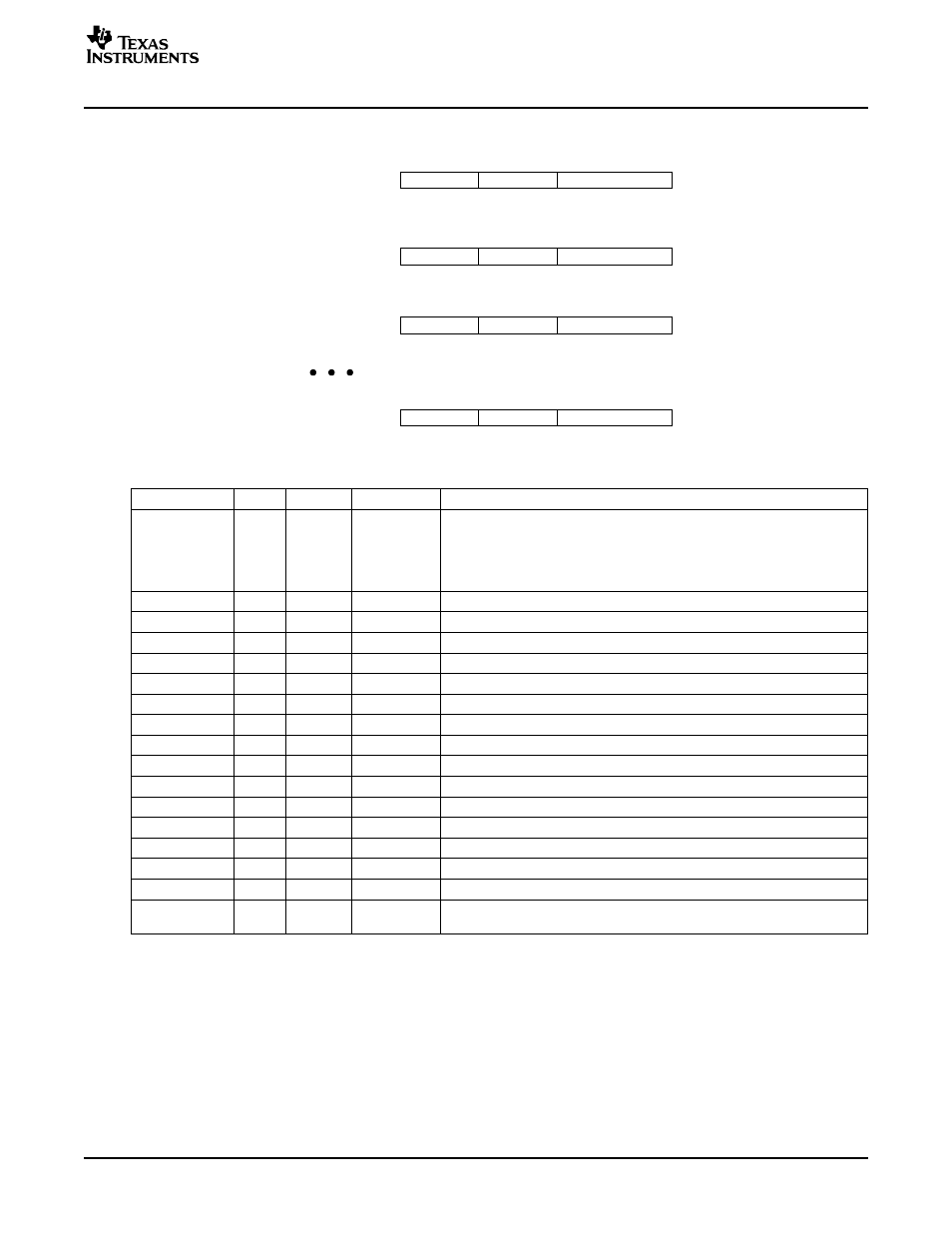

Reserved

RIO_FLOW_CNTL0

31

R, all zeros

tt

17

R/W, 0b01

Flow_Cntl_ID0

15

R/W, 0x0000

Reserved

RIO_FLOW_CNTL1

31

R, all zeros

tt

17

R/W, 0b01

Flow_Cntl_ID1

15

R/W, 0x0000

Reserved

RIO_FLOW_CNTL2

31

R, all zeros

tt

17

R/W, 0b01

Flow_Cntl_ID2

15

R/W, 0x0000

Reserved

RIO_FLOW_CNTL15

31

R, all zeros

tt

17

R/W, 0b01

Flow_Cntl_ID15

15

R/W, 0x0000

SRIO Functional Description

Figure 27. Flow Control Table Entry Registers (Address Offset 0x0900 - 0x093C)

Table 22. Flow Control Table Entry Registers (Address Offset 0x0900 - 0x093C)

Name

Bit

Access

Reset Value

Description

tt

[17:16]

R/W

01b

Selects Flow_Cntl_ID length.

00b – 8b IDs

01b – 16b IDs

10b – 11b - reserved

Flow_Cntl_ID0

[15:0]

R/W

0x0000

DestID of Flow 0

Flow_Cntl_ID1

[15:0]

R/W

0x0000

DestID of Flow 1

Flow_Cntl_ID2

[15:0]

R/W

0x0000

DestID of Flow 2

Flow_Cntl_ID3

[15:0]

R/W

0x0000

DestID of Flow 3

Flow_Cntl_ID4

[15:0]

R/W

0x0000

DestID of Flow 4

Flow_Cntl_ID5

[15:0]

R/W

0x0000

DestID of Flow 5

Flow_Cntl_ID6

[15:0]

R/W

0x0000

DestID of Flow 6

Flow_Cntl_ID7

[15:0]

R/W

0x0000

DestID of Flow 7

Flow_Cntl_ID8

[15:0]

R/W

0x0000

DestID of Flow 8

Flow_Cntl_ID9

[15:0]

R/W

0x0000

DestID of Flow 9

Flow_Cntl_ID10

[15:0]

R/W

0x0000

DestID of Flow 10

Flow_Cntl_ID11

[15:0]

R/W

0x0000

DestID of Flow 11

Flow_Cntl_ID12

[15:0]

R/W

0x0000

DestID of Flow 12

Flow_Cntl_ID13

[15:0]

R/W

0x0000

DestID of Flow 13

Flow_Cntl_ID14

[15:0]

R/W

0x0000

DestID of Flow 14

Flow_Cntl_ID15

[15:0]

R/W

0x0000

DestID of Flow 15, if all 0s this table entry represents all flows other than

flows 0 - 14

Each transmit source, including LSU or Tx CPPI queues, indicates which of the 16 flows it uses by having

a mask register.

illustrates the required 16-bit registers with bit masks. The CPU must configure

these registers upon reset. The default setting is all 1s, indicating that the transmit source supports all

flows. If the register is set to all 0s, the transmit source communicates that it does not support any flow,

and consequently, that source is never flow-controlled. If any of the table entry counters that a transmit

source supports have a corresponding non-zero Xoff count, the transmit source is flow-controlled. A

simple 16-bit bus indicates the Xoff state of all 16 flows and is compared to the transmit source mask

register. Each source interprets this result and performs flow control accordingly. For example, an LSU

module that is flow-controlled can reload its registers and attempt to send a packet to another flow, while a

TX CPPI queue that is flow-controlled may create HOL blocking issues on that queue.

SPRU976 – March 2006

Serial RapidIO (SRIO)

61