Description – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 67

56

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Description

The memory barrier instruction,

MEMBAR

, has two complementary functions: to

express order constraints between memory references and to provide explicit control

of memory-reference completion. The

membar_mask

field in the suggested assembly

language is the concatenation of the

cmask

and

mmask

instruction fields.

The

mmask

field is encoded in bits 3 through 0 of the instruction.

specifies

the order constraint that each bit of

mmask

(selected when set to 1) imposes on

memory references appearing before and after the

MEMBAR

. From zero to four mask

bits can be selected in the

mmask

field.

The

cmask

field is encoded in bits 6 through 4 of the instruction. Bits in the

cmask

field, described in

, specify additional constraints on the order of memory

references and the processing of instructions. If

cmask

is zero, then

MEMBAR

enforces

the partial ordering specified by the

mmask

field; if

cmask

is nonzero, then

completion and partial order constraints are applied.

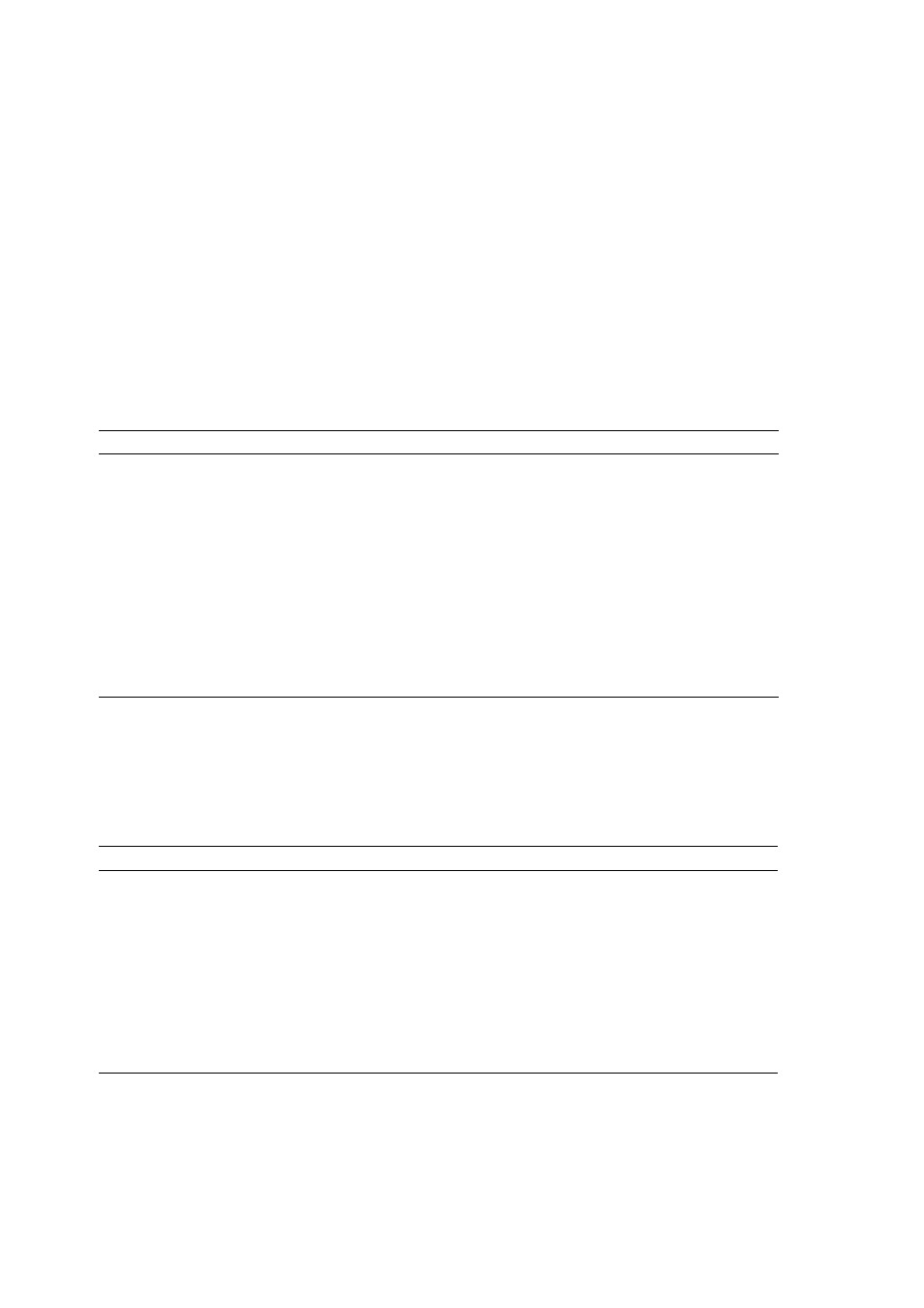

TABLE A-5

Order Constraints Imposed by

mmask

Bits

Mask Bit

Name

Description

mmask

<3>

#StoreStore

The effects of all stores appearing before the

MEMBAR

instruction must be

visible to all processors before the effect of any stores following the

MEMBAR

.

Equivalent to the deprecated

STBAR

instruction. Has no effect on SPARC64 V

since all stores are performed in program order.

mmask

<2>

#LoadStore

All loads appearing before the

MEMBAR

instruction must have been performed

before the effects of any stores following the

MEMBAR

are visible to any other

processor. Has no effect on SPARC64 V since all stores are performed in

program order and must occur after performance of any load.

mmask

<1>

#StoreLoad

The effects of all stores appearing before the

MEMBAR

instruction must be

visible to all processors before loads following the

MEMBAR

may be performed.

mmask

<0>

#LoadLoad

All loads appearing before the

MEMBAR

instruction must have been performed

before any loads following the

MEMBAR

may be performed. Has no effect on

SPARC64 V since all loads are performed after any prior loads.

TABLE A-6

Bits in the

cmask

Field

Mask Bit

Function

Name

Description

cmask

<2>

Synchronization

barrier

#Sync

All operations (including nonmemory reference operations)

appearing before the

MEMBAR

must have been performed, and

the effects of any exceptions become visible before any

instruction after the

MEMBAR

may be initiated.

cmask

<1>

Memory issue

barrier

#MemIssue

All memory reference operations appearing before the

MEMBAR

must have been performed before any memory operation after

the

MEMBAR

may be initiated. Equivalent to

#Sync

in

SPARC64 V.

cmask

<0>

Lookaside

barrier

#

Lookaside

A store appearing before the

MEMBAR

must complete before

any load following the

MEMBAR

referencing the same address

can be initiated. Equivalent to

#Sync

in SPARC64 V.