R.3 upa config register, Upa config register 215 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 226

Release 1.0, 1 July 2002

F. Chapter R

UPA Programmer’s Model

215

R.3

UPA Config Register

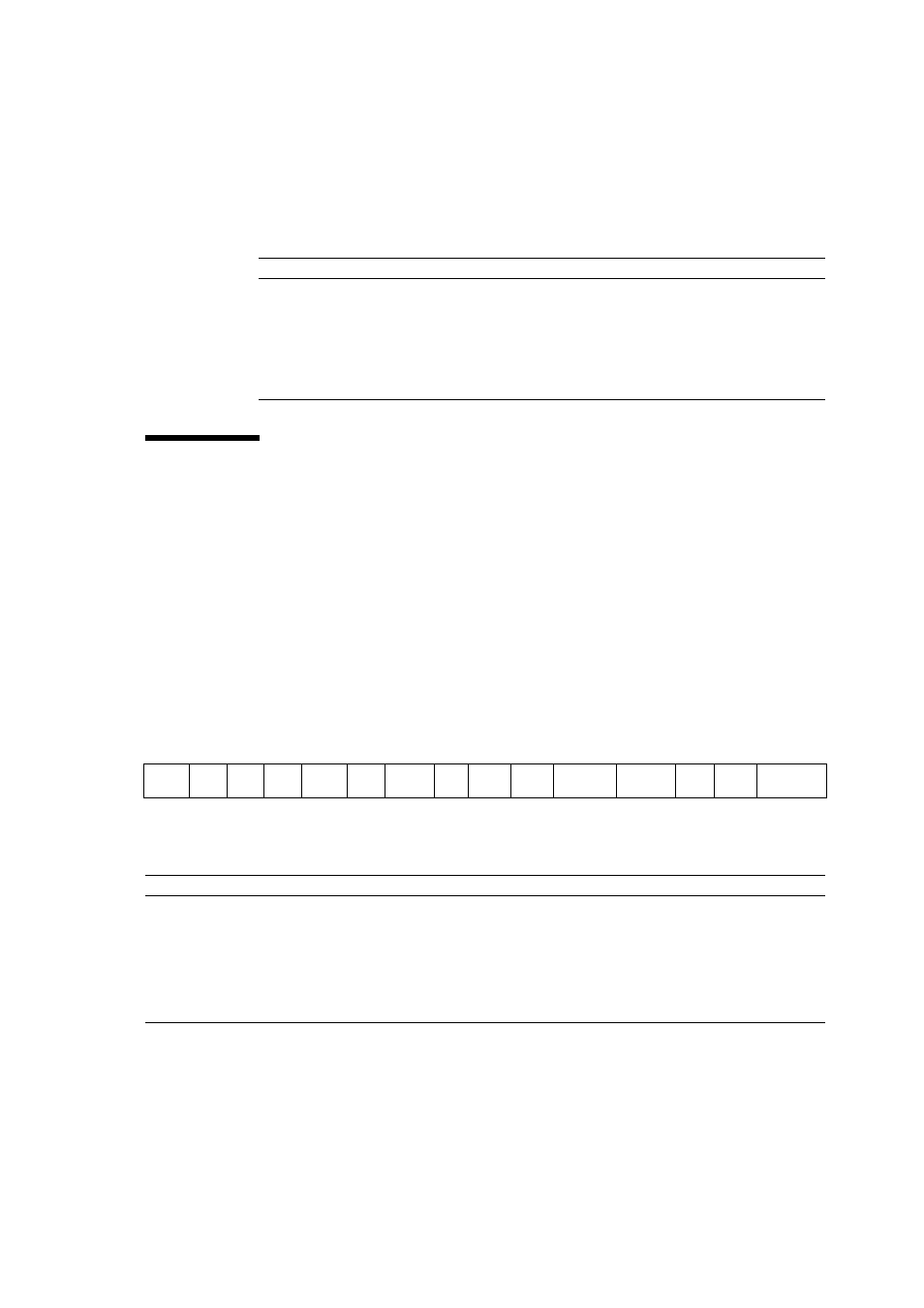

The UPA Config Register is an implementation-specific ASI read-only register. This

register is accessible in the ASI 4A

16

space from the host processor and cannot be

accessed for a UPA slave read.

Bits 16:0 and bit 22 are connected to bits 32:16 and bit 35 of the

UPA_PortId

register,

respectively. Bits 21:17 are connected to the

P_UPA_PORT_ID

4:0 external pins. The

UPA Config Register is illustrated below and described in

.

20:16

UPACAP

UPACAP

<4:0>. Indicates the UPA module capability type, as

follows:

UPACAP

<4> Set; CPU is an interrupt handler.

UPACAP

<3> Set; CPU is an interrupter.

UPACAP

<2> Clear; CPU does not use UPA Slave_Int_L signal.

UPACAP

<1> Set; CPU is a cache master.

UPACAP

<0> Set; CPU has a master interface.

[1]

Register Name:

ASI_UPA_CONFIGURATION_REGISTER

[2]

ASI:

4A

16

[3]

VA:

0

[4]

RW

Supervisor read, a write is ignored.

[5]

Data

Reserved

WB_S WRI_

S

INT_S

Reserved

UC_S

Reserved

AM

MCAP

Reserved

CLK_MODE

PCON

UPC_

CAP2

MID

UPC_CAP

63

62 61

59 58

57 56 55 54

46 45

43 42

41 40 39 38

35

34

33

30 29

23

22

21

17 16

0

TABLE R-3

UPA Config Register Description

Bits

Field

Description

63:62

—

Reserved. Read as 0.

61:59

WB_S

Specify the size of maximum outstanding writeback (

RD

x with

DVP

) as follows.

000

2

:

1

001

2

:

2

010

2

:

4

011

2

:

8

100

2

– 111

2

:

8 but should not be specified for the extension.

TABLE R-2

UPA PortID Register Fields (Continued)

Bit

Field

Description