FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 114

Release 1.0, 1 July 2002

F. Chapter F

Memory Management Unit

103

Multiple bits of

DSFSR.FT

may be set by a trap as long as the cause of the trap

.

DSFSR

is updated upon various traps, including

f

ast_data_access_MMU_miss

,

data_access_exception

,

fast_data_access_protection

,

PA_watchpoint

,

VA_watchpoint

,

privileged_action

,

mem_address_not_aligned

, and

data_access_error

traps.

shows the detailed update policy of each field.

08

16

An attempt was made to access an alternate address space with an illegal ASI

value, an illegal VA, an invalid read/write attribute, or an illegally sized

operand. If the quad load ASI is used with the other opcode than

LDDA

, this bit

is set.

Note:

Since an illegal ASI check is done prior to a TTE unmatch check,

DSFSR.FT<3>

= 1 causes the value of other bits of

DSFSR.FT

to be

undetermined and generates a

data_access_exception

exception (which

otherwise has lower priority than

fast_data_access_MMU_miss

).

Note, too, that a reference to an internal ASI may generate a

mem_address_not_aligned

exception.

10

16

Access other than nonfaulting load was made to a page marked

NFO

. This bit is

zero for internal ASI accesses.

20

16

Reserved, since there is no virtual hole.

40

16

Reserved, since there is no virtual hole.

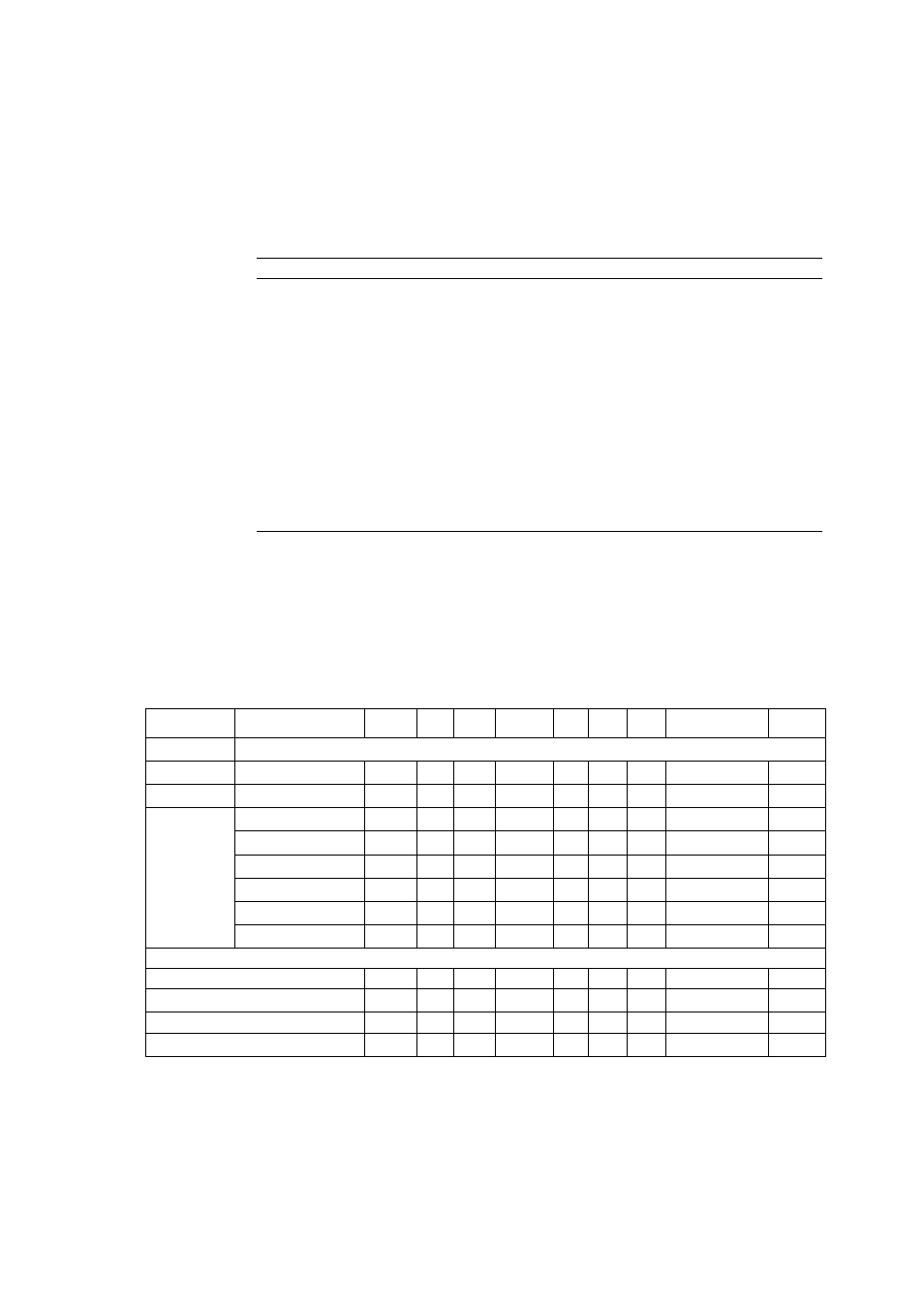

TABLE F-10

DSFSR

Update Policy

Field

TLB#,

index

FV

OW

W, PR,

NF, CT

1

FT

TM

ASI

UE, UPA,

mDTLB, NC

2

, E

DSFAR

Fresh fault or miss

3

Miss

MMU miss

—

0

0

V

—

1

—

—

V

Exception

Access exception

—

1

0

V

V

0

V

—

V

Faults

Access protection

—

1

0

V

—

0

V

—

V

PA watchpoint

—

1

0

V

—

0

V

—

V

VA watchpoint

—

1

0

V

—

0

V

—

V

Privileged action

4

—

1

0

V

—

0

V

—

V

Access misaligned

—

1

0

V

—

0

V

—

-

V

Access error

V

5

1

0

V

—

0

V

V

V

Overwrite Policy

6

Exception on fault

K

1

1

U

U

K

U

K

U

Fault on exception

U

1

1

U

K

K

U

U

U

Exception on miss

7

K

1

K

U

U

1

U

K

U

Fault on miss

U

1

K

U

K

1

U

U

U

TABLE F-9

MMU Synchronous Fault Status Register

FT

(Fault Type) Field (Continued)

FT<6:0>

Error Description