M.3.2 level-2 cache control register (asi_l2_ctrl), Level-2 cache control register (asi_l2_ctrl) 13, L2 diagnostics tag read (asi_l2_diag_tag_read) 130 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 141

130

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

M.3.2

Level-2 Cache Control Register (

ASI_L2_CTRL

)

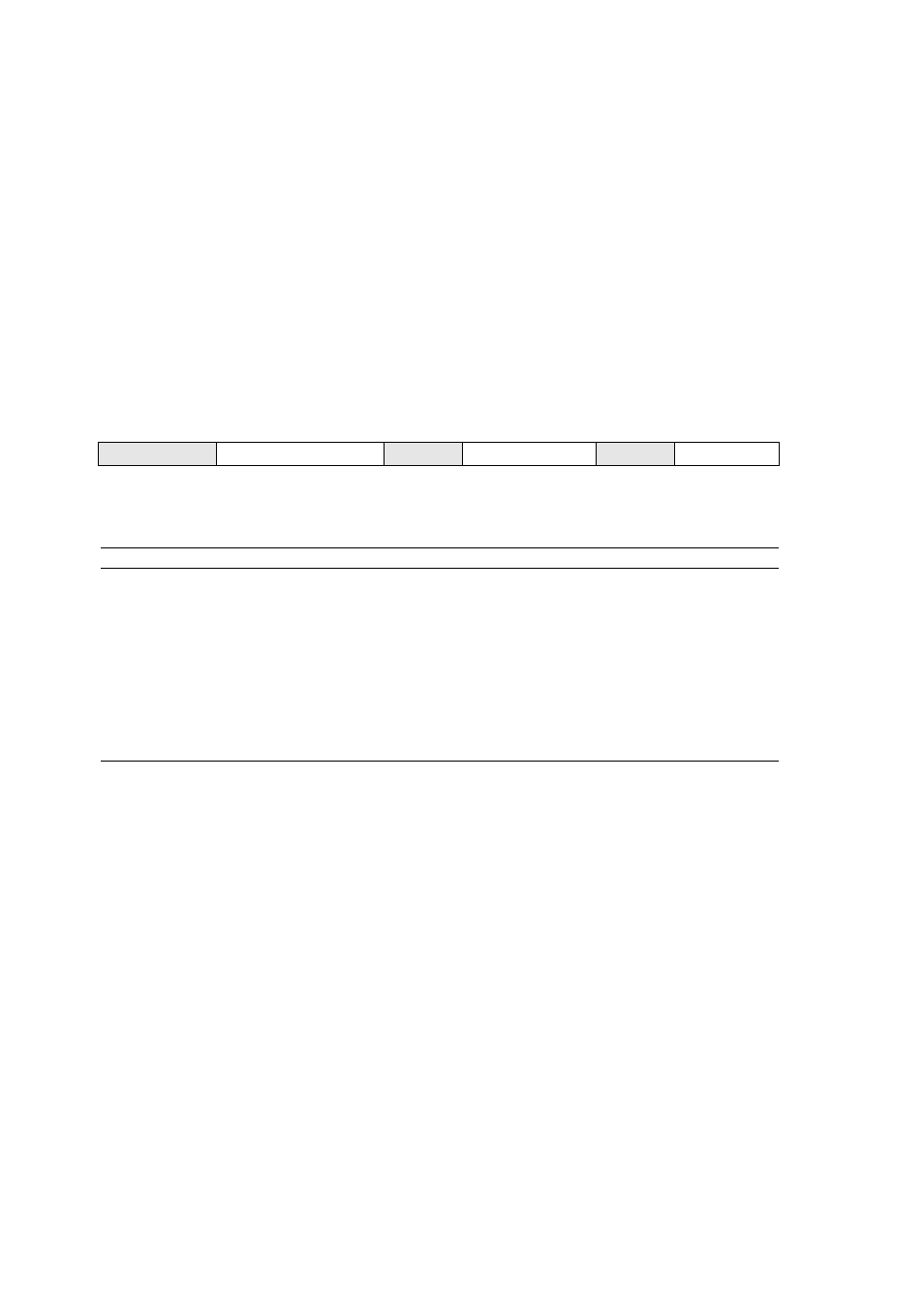

ASI_L2_CTRL

is a control register for L2 training, interface, and size configuration.

It is illustrated below and described in

.

M.3.3

L2 Diagnostics Tag Read

(

ASI_L2_DIAG_TAG_READ

)

This ASI instruction is a diagnostic read of L2 cache tag, as well as tag 2 of L1I and

L1D.

[1]

Register Name:

ASI_L2_CTRL

[2]

ASI:

6A

16

[3]

VA:

10

16

[4]

RW

Supervisor read/write

[5]

Data

Reserved

URGENT_ERROR_TRAP

Reserved

NUMINSWAY

Reserved

U2_FLUSH

63

25

24

23

19

18

16

15

1

0

TABLE M-6

ASI_L2_CTRL

Register Bits

Bit

Field

RW

Description

24

URGENT_ERROR_TRAP

RW1C

This bit is set to 1 when one of the error exceptions

(

instruction_access_error

,

data_access_error

, or

asynchronous_data_error

)

exception is generated. The bit remains set to 1 until supervisor

software explicitly clears it by writing 1 to the bit.

18:16

NUMINSWAY

R

Set associativity of L2 cache, as follows:

2

2-way mode

4:

4-way mode

0

U2_FLUSH

W

Flush the entire level-2 cache. The flushing takes approximately 10

ms, Until the flushing of the level-2 cache completes, the processor

ceases operation and does not perform further instruction

execution.