F.10.7 i/d tsb extension registers, Section f.10.9, I/d tsb base registers – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 108

Release 1.0, 1 July 2002

F. Chapter F

Memory Management Unit

97

I/D TSB Base Registers

IMPL. DEP. #236

:

The width of the

TSB_Size

field in the TSB Base Register is

implementation dependent; the permitted range is from 2 to 6 bits. The least

significant bit of

TSB_Size

is always at bit 0 of the TSB Base Register. Any bits

unimplemented at the most significant end of

TSB_Size

read as 0, and writes to

them are ignored.

On SPARC64 V, the width of the

TSB_Size

field in the TSB Base Register is 4

bits. The number of entries in the TSB ranges from 512 entries at

TSB_Size

= 0 (8

Kbytes for common TSB, 16 Kbytes for split TSB), to 16 million entries at

TSB_Size

= 15 (256 Mbytes for common TSB, 512 Mbytes for split TSB).

F.10.7

I/D TSB Extension Registers

IMPL DEP. in Commonality

FIGURE

F-13:

Bits 11:3 in I/D TSB Extension Register

are an implementation-dependent field.

On SPARC64 V, bits 11:0 in I/D TSB Extension Registers are assigned as follows.

■

Bits 11:4 — Reserved. Always read as 0, and writes to it are ignored.

■

Bits 3:0 —

TSB_Size

field is expanded to be a 4-bit field in SPARC64 V.

F.10.9

I/D Synchronous Fault Status Registers (I-SFSR,

D-SFSR)

IMPL DEP. in Commonality

FIGURE

F-15 and

TABLE

F-12:

Bits 63:25 in I/D

Synchronous Fault Status Registers (

I-SFSR

,

D-SFSR

) are an implementation-

dependent field.

The format of I/D-MMU

SFSR

in SPARC64 V is shown in

.

FIGURE F-3

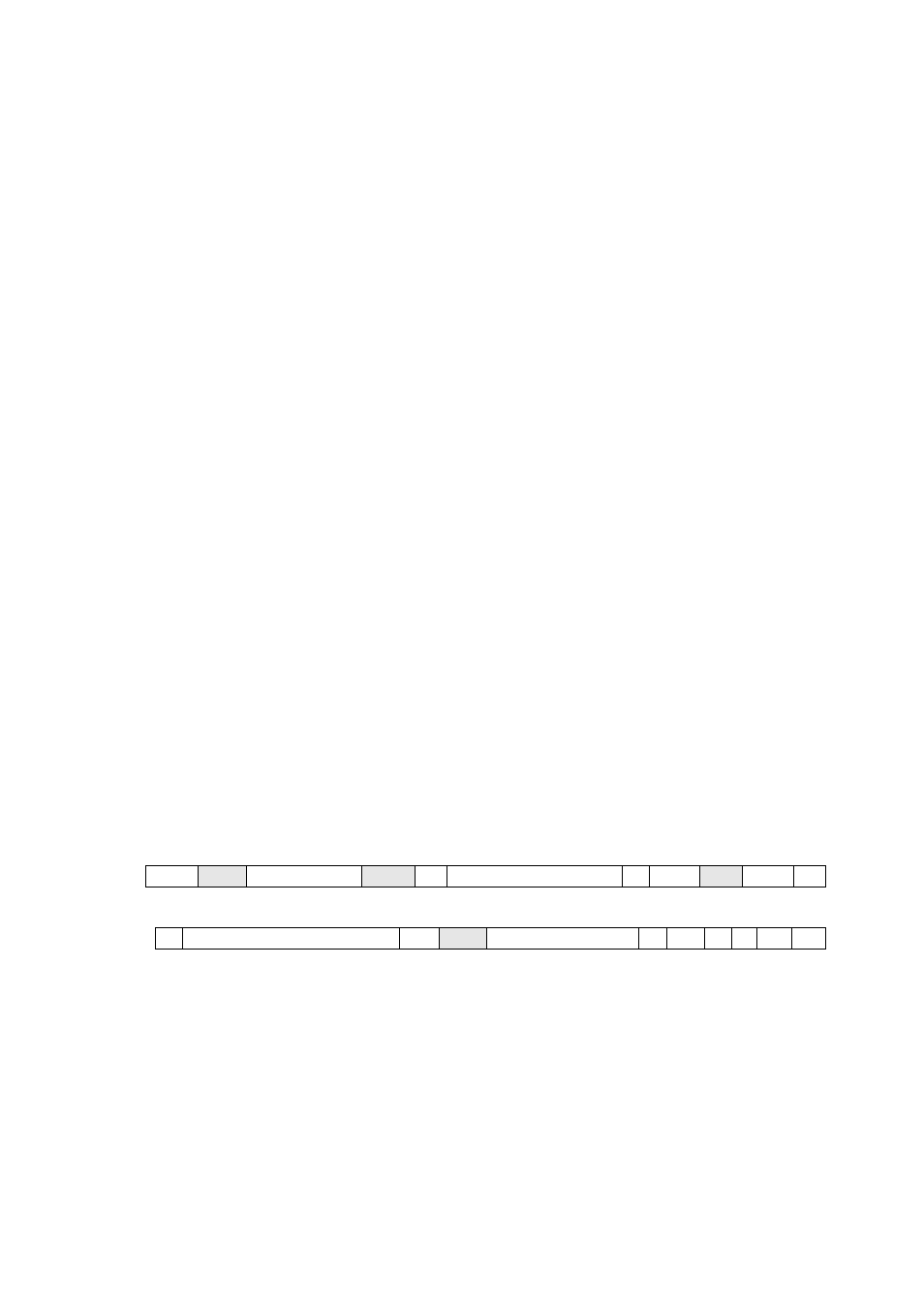

MMU I/D Synchronous Fault Status Registers (

I-SFSR

,

D-SFSR

)

TLB #

reserved

index

reserved

MK

EID

UE

UPA

reserved

mTLB

NC

63

62 61

60 59

49 48

47

46

45

32 31 30

29

28

27

26

25

NF

ASI

TM

reserved

FT

E

CT

PR

W

OW

FV

24 23

16

15

14

13

7

6

5

4

3

2

1

0