P.8 handling of internal register errors, Handling of internal register errors 181, P.8.1 an – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 192

Release 1.0, 1 July 2002

F. Chapter P

Error Handling

181

P.8

Handling of Internal Register Errors

This section describes error handling for the following:

■

Most registers

■

ASR registers

■

ASI registers

P.8.1

Register Error Handling (Excluding ASRs and ASI

Registers)

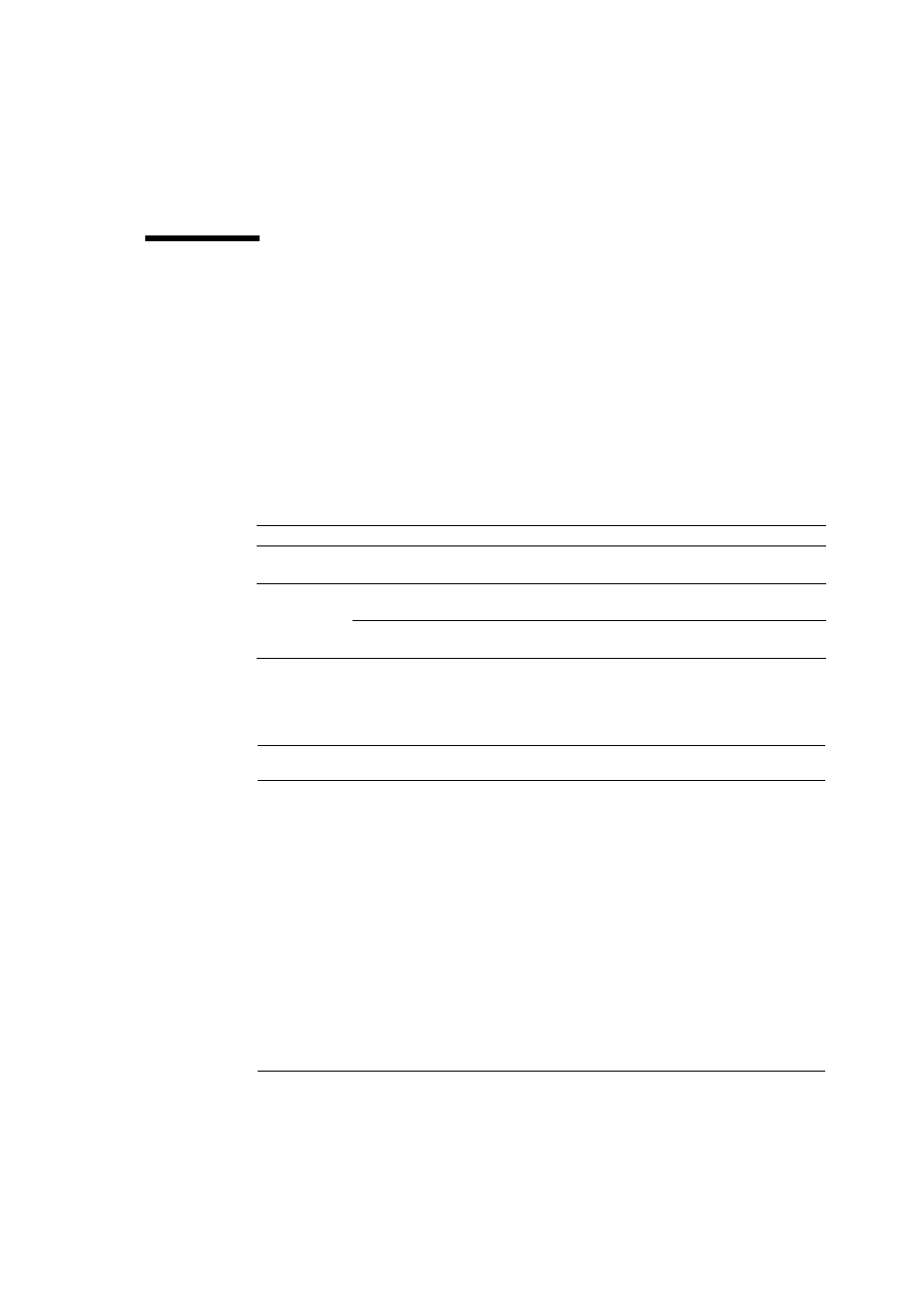

The terminology used in

shows error handling for most registers.

Column

Term

Meaning

Error Detect

Condition

InstAccess

The error is detected when the instruction accesses the register.

Correction

W

The error indication is removed when an instruction performs a

full write to the register

ADE

trap

The error is removed by a full write to the register in the

async_data_error

hardware trap sequence.

TABLE P-18

Register Error Handling (Excluding ASRs and ASI Registers)

Register Name

RW

Error

Protect

Error Detect Condition

Error Type

Correction

%r

n

RW

Parity

InstAccess

IUG_%R

W

%f

n

RW

Parity

InstAccess

IUG_%F

W

PC

Parity

Always

IUG_PSTATE

ADE

trap

nPC

Parity

Always

IUG_PSTATE

ADE

trap

PSTATE

RW

Parity

Always

IUG_PSTATE

ADE

trap

TBA

RW

Parity

PSTATE.RED

= 0

error_state

W (by

OBP

)

PIL

RW

Parity

PSTATE.IE

= 1

or InstAccess

IUG_PSTATE

W

CWP

,

CANSAVE

,

CANRESTORE

,

OTHERWIN

,

CLEANWIN

RW

Parity

Always

IUG_PSTATE

ADE

trap, W

TT

RW

None

—

—

—

TL

RW

Parity

PSTATE.RED

= 0

error_state

W (by

OBP

)