FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 231

220

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

Floating-point

subnormal

handling

In general, SPARC64 V does not

handle most subnormal operands

and results in hardware. However,

its handling differs from that of

UltraSPARC-III.

In general, UltraSPARC-III does

not handle most subnormal

operands and results in

hardware. However, its handling

differs from that of SPARC64 V.

B.6.1

Block LD/ST

implementation

SPARC64 V maintains register

dependency between block load/

store and other instructions, but

hardware memory order constraint

is less than TSO.

UltraSPARC-III does not

necessarily preserve memory or

register dependency ordering in

block load/store operations.

A.4

PREFETCH

(

A

)

implementation

Prefetch-invalidate is not

implemented—SPARC64 V does

not implement a P-cache.

Prefetch with

fcn

= 20-23 causes a

trap on mDTLB miss.

Implements prefetch-invalidate

(

fcn

= 16).

fcn

= 20-23 does not cause a

trap. Equivalent to

fcn

= 0-3.

A.49.1

Data cache

flushing

Because SPARC64 V supports

unaliasing by hardware, a flush of

data cache is not needed.

—

Because the data cache uses one

virtual address bit for indexing, a

displacement flushing algorithm

or a cache diagnostic write is

required when a virtual address

alias is created.

1.4.4, M.2

TPC

/

TNPC

state

after power-on

reset

Both

TPC

and

TNPC

values are

undefined after a power-on reset.

TPC

<5:0> is zero after any reset

trap.

TNPC

will be equal to

TNPC+4

.

C.2.5

W-cache

SPARC64 V does not support a W-

cache.

ASIs 38

16

–3B

16

provide

diagnostic access to the W-cache.

L.3.2

P-cache

SPARC64 V does not support a

P-cache.

ASIs 30

16

–33

16

provide diagnostic

access to the P-cache.

L.3.2

UPA

Configuration

ASI

SPARC64 V uses ASI 4A

16

as the

UPA configuration register.

UltraSPARC-III does not support

UPA. Fireplane configuration

register is assigned in ASI 4A

16

.

R.2

SRAM test init

Not supported.

—

ASI 40

16

: not defined in manual. —

D-cache

Not supported.

—

ASIs 42

16

through 47

16

support

data cache diagnostic access.

L.3.2

E-cache

ASIs 6B

16

and 6C

16

support E-

cache diagnostic access.

ASIs 4B

16

, 4E

16

, 74

16

, 75

16

, 76

16

,

and 7E

16

support control over the

E-cache.

L.3.2

ASI_AFSR

Many differences.

Many differences.

P.4.2

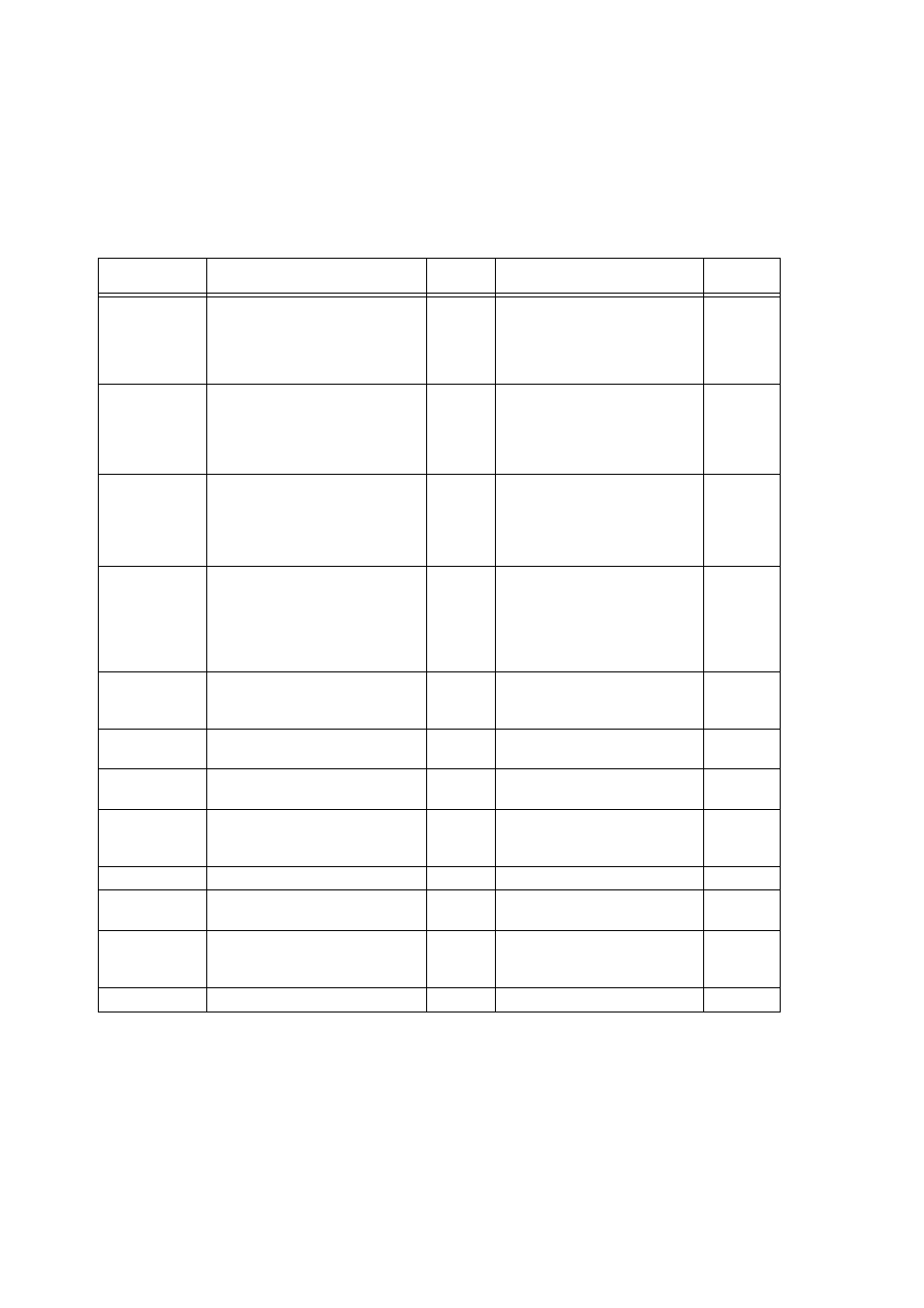

TABLE T-1

SPARC64 V and UltraSPARC-III Differences

(2 of 3)

Feature

SPARC64 V

SPARC64 V

Page

UltraSPARC-III

UltraSPARC-

III Section