A.24.1 floating-point multiply-add/subtract, Floating-point multiply-add/subtract 50, Format (5) – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 61

50

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

A.24.1

Floating-Point Multiply-Add/Subtract

SPARC64 V uses

IMPDEP2B

opcode space to encode the Floating-Point Multiply

Add/Subtract instructions.

† 11 is reserved for quad.

Format (5)

Opcode

Variation

Size†

Operation

FMADDs

00

01

Multiply-Add Single

FMADDd

00

10

Multiply-Add Double

FMSUBs

01

01

Multiply-Subtract Single

FMSUBd

01

10

Multiply-Subtract Double

FNMADDs

11

01

Negative Multiply-Add Single

FNMADDd

11

10

Negative Multiply-Add Double

FNMSUBs

10

01

Negative Multiply-Subtract Single

FNMSUBd

10

10

Negative Multiply-Subtract Double

Operation

Implementation

Multiply-Add

rd

←

rs1

×

rs2

+

rs3

Multiply-Subtract

rd

←

rs1

×

rs2

−

rs3

Negative Multiply-Subtract

rd

←

−

(

rs1

×

rs2

−

rs3

)

Negative Multiple-Add

rd

←

−

(

rs1

×

rs2

+

rs3

)

Assembly Language Syntax

fmadds

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fmaddd

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fmsubs

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fmsubd

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fnmadds

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fnmaddd

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fnmsubs

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

fnmsubd

freg

rs1

, freg

rs2

, freg

rs3

, freg

rd

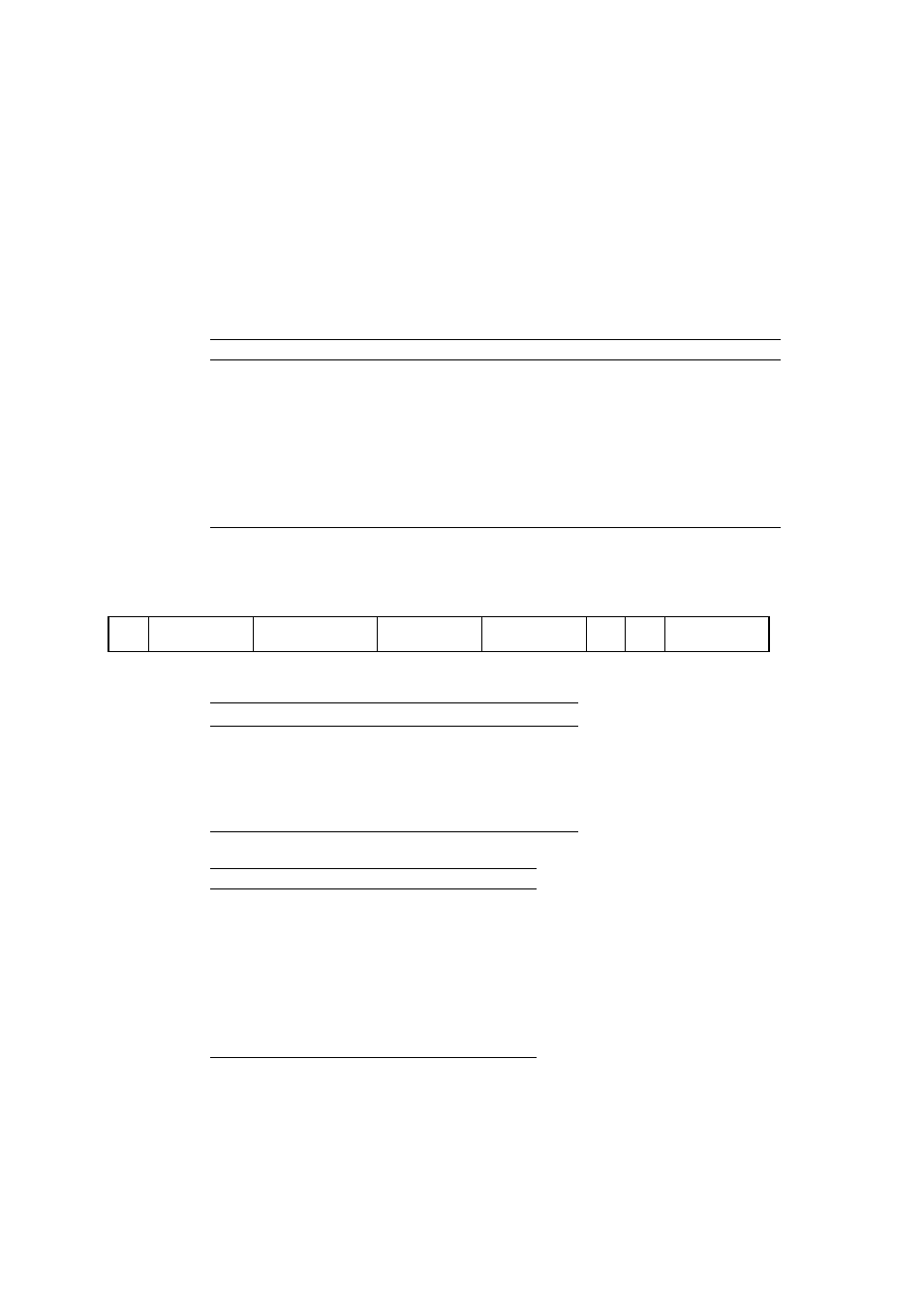

10

110111

rs2

rd

31

18

24

0

25

30 29

19

4

5

6

7

8

9

13

14

size

var

rs3

rs1