3 syncing instructions, Syncing instructions 27 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 38

Release 1.0, 1 July 2002

F. Chapter 6

Instructions

27

6.1.3

Syncing Instructions

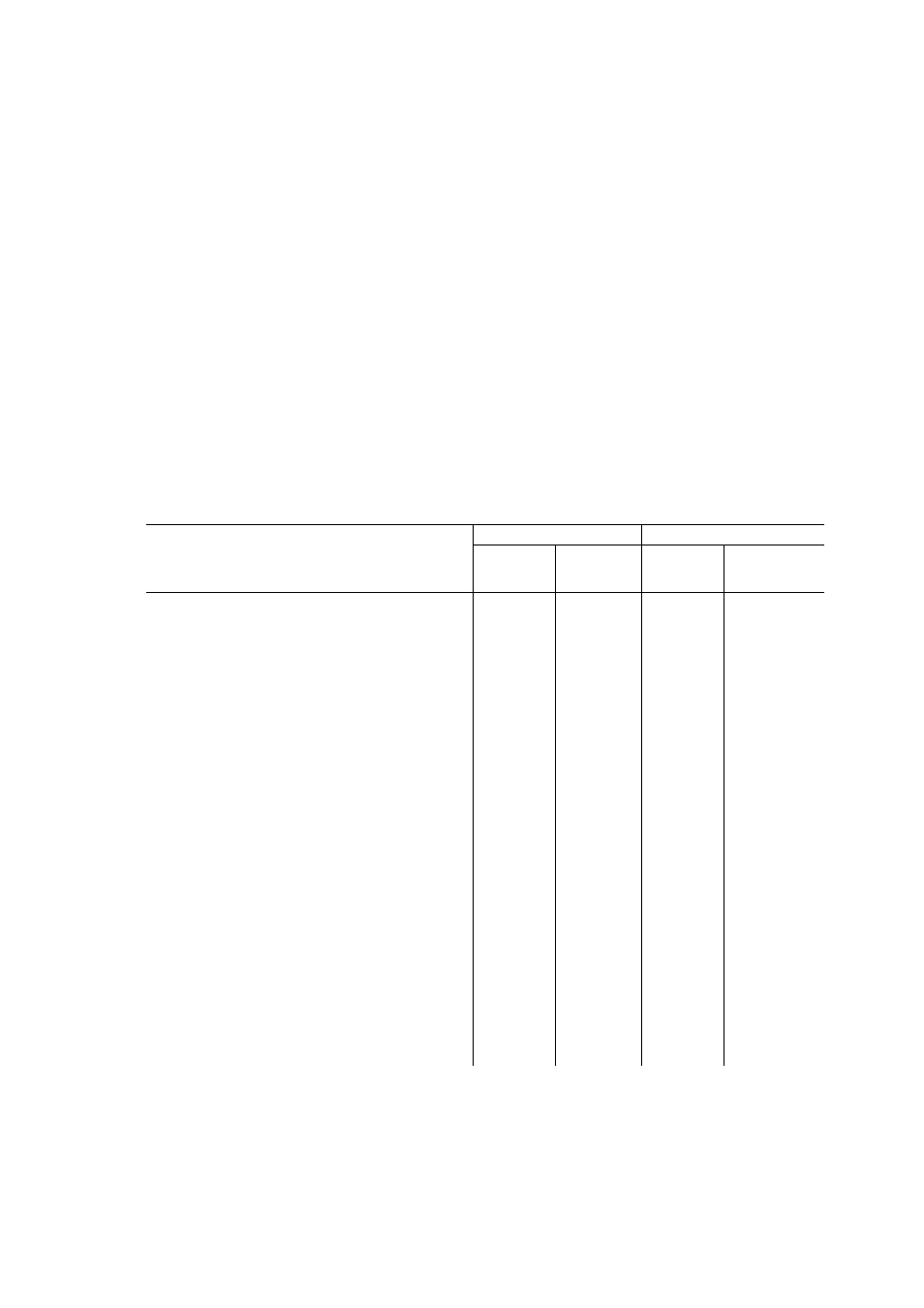

SPARC64 V has instructions, called syncing instructions, that stop execution for the

number of cycles it takes to clear the pipeline and to synchronize the processor.

There are two types of synchronization, pre and post. A presyncing instruction waits

for all previous instructions to commit, commits by itself, and then issues successive

instructions. A postsyncing instruction issues by itself and prevents the successive

instructions from issuing until it is committed. Some instructions have both pre- and

postsync attributes.

In SPARC64 V almost all instructions commit in order, but store instruction commit

before becoming globally visible. A few syncing instructions cause the processor to

discard prefetched instructions and to refetch the successive instructions.

lists all pre-/postsync instructions and the effects of instruction execution.

TABLE 6-1

SPARC64 V Syncing Instructions

Opcode

Presyncing

Postsyncing

Sync?

Wait for

store global

visibility?

Sync?

Discard

prefetched

instructions?

ALIGNADDRESS{_LITTLE}

Yes

BMASK

Yes

DONE

Yes

Yes

FCMP

(

GT

,

LE

,

NE

,

EQ

)(

16

,

32

)

Yes

FLUSH

Yes

Yes

Yes

FMOV

(

s

,

d

)

icc

Yes

FMOVr

Yes

LDD

Yes

Yes

LDDA

Yes

Yes

LDDFA

Yes

memory access with

ASI=ASI_PHYS_BYPASS_EC{_LITTLE}

,

ASI_PHYS_BYPASS_EC_WITH_E_BIT{_LITTLE}

Yes

LDFSR

,

LDXFSR

Yes

MEMBAR

Yes

Yes

1

Yes

MOVfcc

Yes

MULScc

Yes

PDIST

Yes

RDASR

Yes

RETRY

Yes

Yes

SIAM

Yes

STBAR

Yes

STD

Yes