F.10 internal registers and asi operations, F.10.1 accessing mmu registers, Internal registers and asi operations 92 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 103: Accessing mmu registers 92

92

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

F.10

Internal Registers and ASI operations

F.10.1

Accessing MMU Registers

IMPL. DEP. #233

:

Whether the

TSB_Hash

field is implemented in I/D

Primary/Secondary/Nucleus TSB Extension Register is implementation dependent

in JPS1.

On SPARC64 V, the

TSB_Hash

field is not implemented in the I/D

Primary/Secondary/Nucleus TSB Extension Register. See TSB Pointer Formation

on page 88 for details.

IMPL. DEP. #239

:

The register(s) accessed by IMMU ASI 55

16

and DMMU ASI 5D

16

at

virtual addresses 40000

16

to 60FF8

16

are implementation dependent.

See impl. dep. #235 in I/D TLB Data In, Data Access, and Tag Read Registers on page

93.

Additional information:

The

ASI_DCUCR

register also affects the MMUs.

ASI_DCUCR

is described in Section 5.2.12 of Commonality. The SPARC64 V

implementation dependency in

ASI_DCUCR

is described in Data Cache Unit Control

SPARC64 V also has an additional MMU internal register

ASI_MCNTL

(Memory

Control Register) that is shared between the IMMU and the DMMU. The register is

illustrated in

and described in

ASI_MCNTL (Memory Control Register)

ASI:

45

16

VA:

08

16

Access Modes: Supervisor read/write

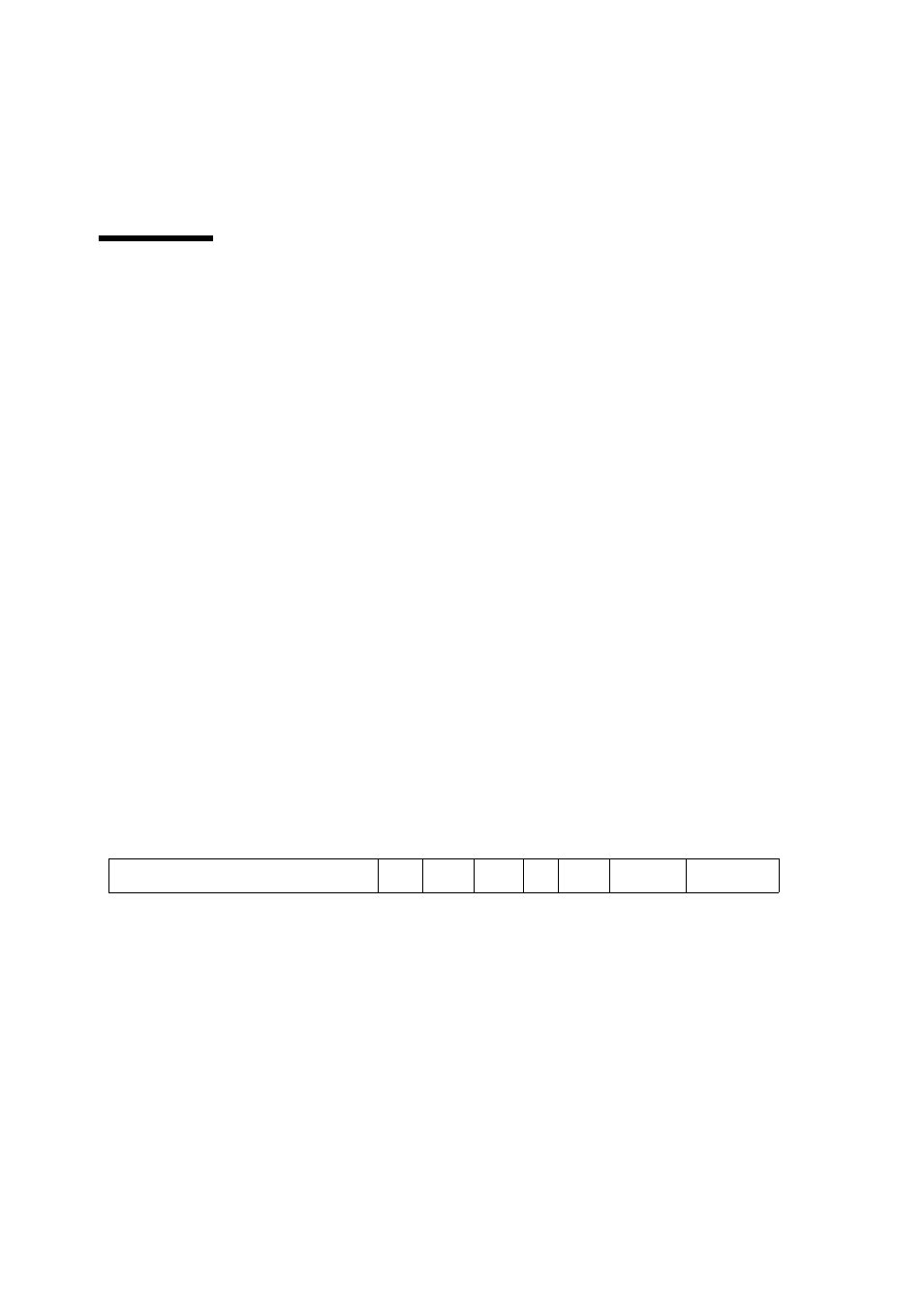

FIGURE F-1

Format of

ASI_MCNTL

reserved

NC_

Cache

fw_

fITLB

fw_

fDTLB

RMD

000

JPS1_TSBP

00000000

63

17

16

15

14

13 12 11

9

8

7

0