O.3.1 operating status register (opsr), Operating status register (opsr) 146, O.3.1 operating status register ( opsr ) – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 157

146

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

O.3.1

Operating Status Register (

OPSR

)

OPSR

is the control register in the CPU that is scanned in during the hardware

power-on reset sequence before the CPU starts running.

The value of the

OPSR

is specified outside of the CPU and is never changed by

software.

OPSR

is set by scan-in during hardware power-on reset and by a JTAG

command after hardware POR.

Most of

OPSR

setting is not visible for software. However, some

OPSR

values control

the software-visible action.

The following items are controlled by

OPSR

and are visible to software.

1. Initial value of the physical address mode.

The hardware POR initial value of the 41-bit PA mode or 43-bit PA mode is

specified by

OPSR

and set in

UPA_CONFIG.AM

field. In 41-bit PA mode, all

physical addresses issued by the CPU are masked to 41 bits. Otherwise, the CPU

operates in 43-bit PA mode, and physical addresses issued by CPU are masked to

43 bits.

2. The value of

UPA_configuration_register.MCAP

field.

OPSR

can be set so that when

error_state

is entered, the processor remains

halted in

error_state

instead of generating a

watchdog_reset

(impl. dep. #254).

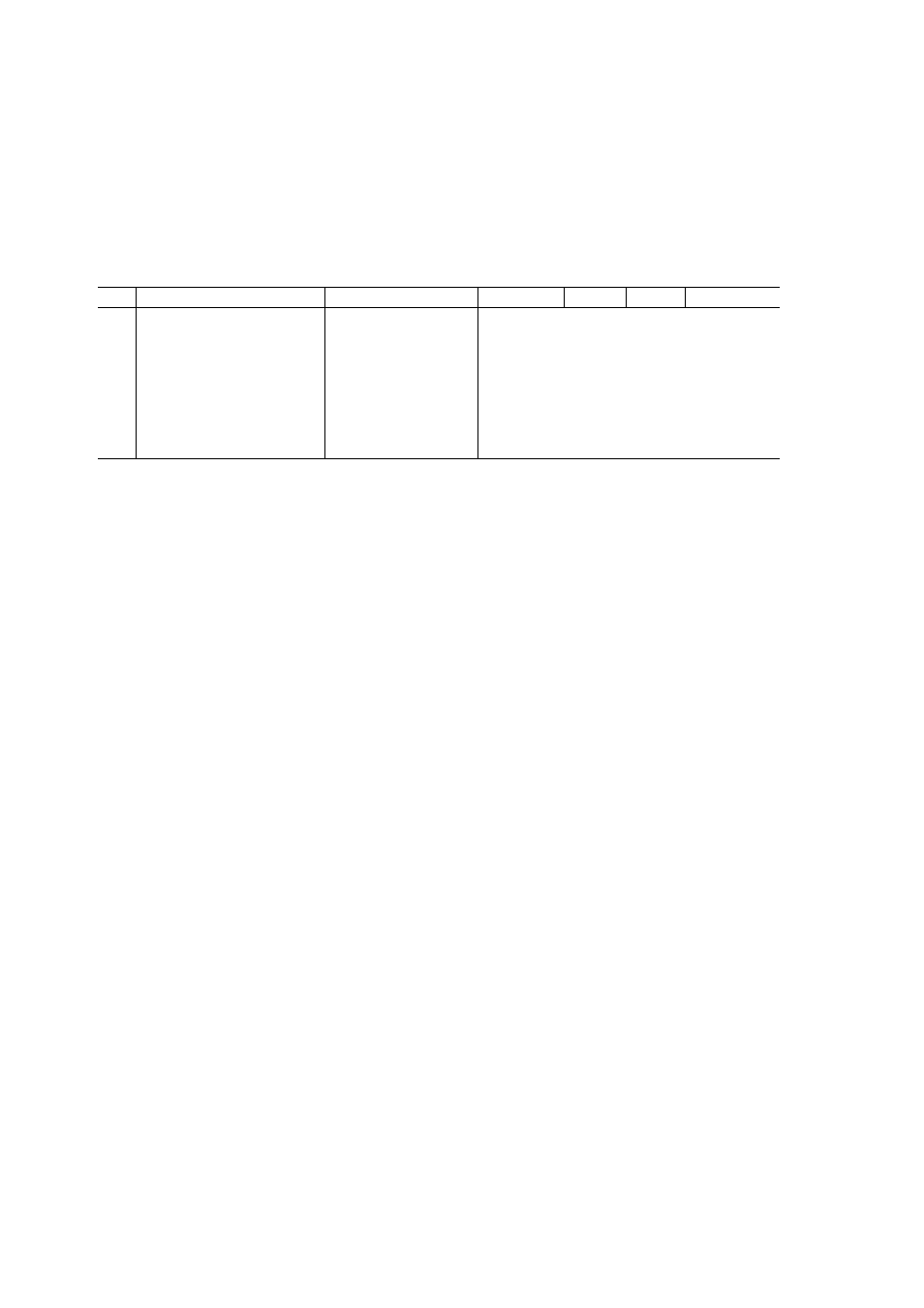

TABLE O-4

UPA slave register State after Reset and in RED_state

PA

Name

POR

1

(binary)

1.Hard POR occurs when power is cycled. Values are unknown following hard POR. Soft POR occurs when

UPA_RESET_L is asserted. Values are unchanged following soft POR.

WDR

2

2.The first watchdog timeout trap is taken in execute_state (i.e.

PSTATE.RED

= 0), subsequent watchdog timeout

traps as well as watchdog traps due to a trap @

TL

=

MAX_TL

are taken in

RED_state

dog Reset (WDR), on page 138 for more details.

XIR

SIR

RED_state

00

UPA_PORTID

Cookie

SREQ_S

ECCnotValid

One_Read

PRINT_RDQ

PREQ_DQ

PREQ_RQ

UPACAP

FC

16

1

0

0

01

000000

0001

11011

Unchanged

Unchanged

Unchanged

Unchanged

Unchanged

Unchanged

Unchanged

Unchanged