FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 154

Release 1.0, 1 July 2002

F. Chapter O

Reset, RED_state, and error_state

143

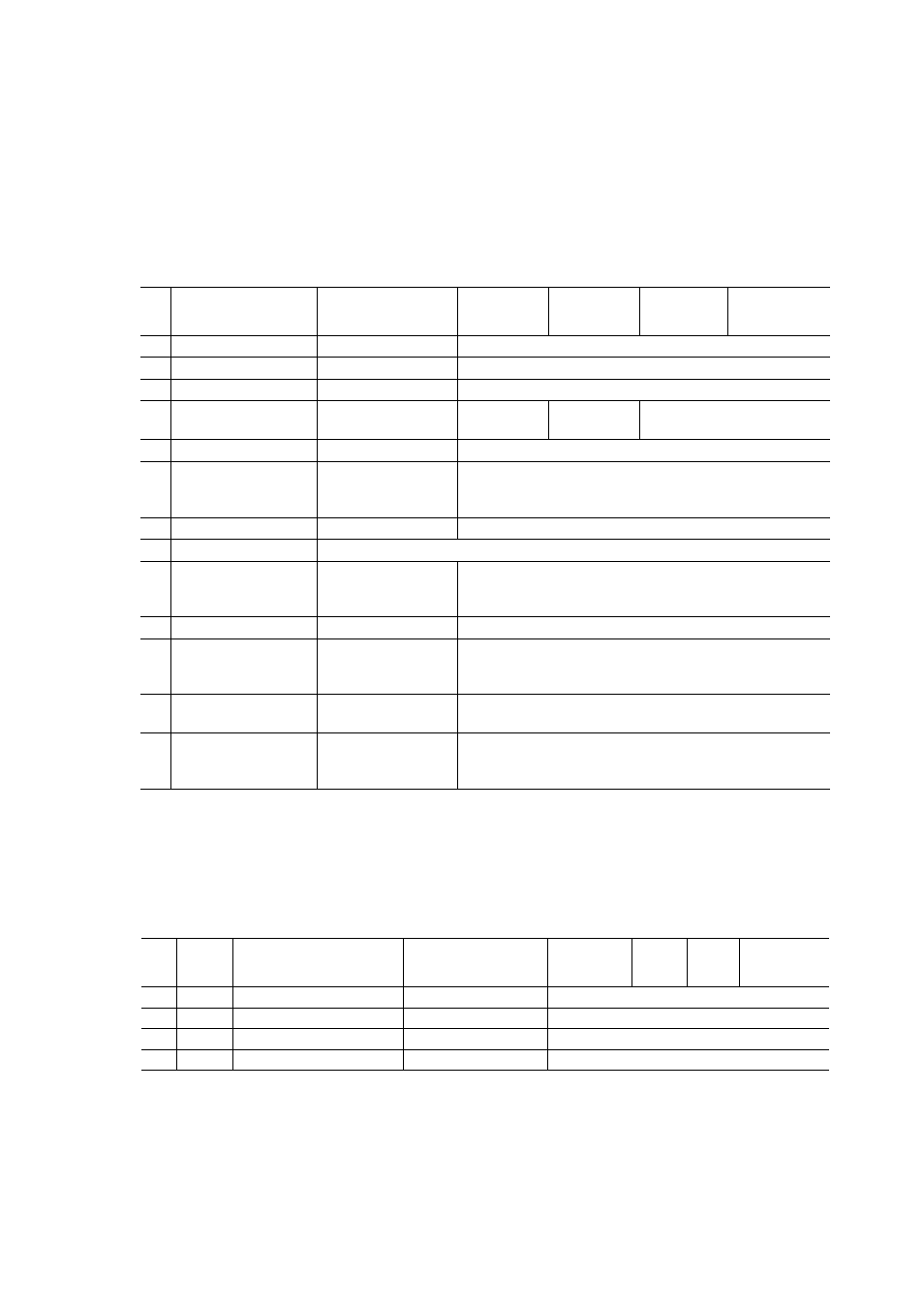

TABLE O-2

ASR State after Reset and in RED_state

A

S

R

Name

POR

1

1.Hard POR occurs when power is cycled. Values are unknown following hard POR. Soft POR occurs when

UPA_RESET_L is asserted. Values are unchanged following soft POR.

WDR

2

2.The first watchdog timeout trap is taken in execute_state (i.e.

PSTATE.RED

= 0), subsequent watchdog timeout

traps as well as watchdog traps due to a trap @

TL

=

MAX_TL

are taken in

RED_state

Reset (WDR), on page 138or more details

XIR

SIR

RED_state

0

Y

Unknown/Unchanged

Unchanged

2

CCR

Unknown/Unchanged

Unchanged

3

ASI

Unknown/Unchanged Unchanged

4

TICK

NPT

Counter

1

Restart at 0

Unchanged

Unchanged

Unchanged

Restart at 0

Unchanged

Unchanged

6

FSR

0

Unchanged

16

PCR

UT

ST

Others

0

0

Unknown/Unchanged

Unchanged

17

PIC

Unknown/Unchanged

Unchanged

18

DCR

Always 0

19

GSR

IM

STE

O

thers

0

0

Unknown/Unchanged

Unchanged

Unchanged

Unchanged

22

SOFTINT

Unknown/Unchanged

Unchanged

23

TICK_COMPARE

INT_DIS

TICK_CMPR

1

0

Unchanged

Unchanged

24

STICK

NPT

Counter

1

Restart at 0

Unchanged

Unchanged (count)

25

STICK_COMPARE

INT_DIS

TICK_CMPR

1

0

Unchanged

Unchanged

TABLE O-3

ASI Register State After Reset and in

RED_state

(1 of 3)

A

S

I

VA

Name

POR

1

WDR

2

XIR

SIR

RED_state

45

00

DCUCR

0

0

45

08

MCNTL

0

0

48

00

INST_BREAKPOINT

0 (off)

Unchanged

49

00

INTR_RECEIVE

Unknown/Unchanged

Unchanged