P.7.4 expected, Software handling of restrainable errors – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 190

Release 1.0, 1 July 2002

F. Chapter P

Error Handling

179

P.7.4

Expected

Software Handling of Restrainable

Errors

Error recording and information is expected for all restrainable errors.

The expected software recovery from each type of each restrainable error is

described below.

■

ASI_AFSR.DG_L1$U2$STLB

— The following status for the CPU is reported:

■

Performance is degraded by the way reduction in

I1$

,

D1$

,

U2$

,

sITLB

, or

sDTLB

.

■

CPU availability may be slightly down. If only one way facility is available

among

I1$

,

D1$

,

U2$

,

sITLB

, and

sDTLB

and further way reduction is

detected for this facility, the

error_state

transition error is detected.

Software stops the use of the CPU, if required.

■

ASI_AFSR.CE_INCOMED

— If

ASI_AFAR_U2

contains

CE_INCOMED

information

and the physical address of the error indicates the cacheable area, the following

software sequence to correct the memory block is expected:

a. Make the U2 cache line with the

CE

detection dirty without changing the data.

Use the

CASA

instruction to write that same data to the U2 cache line.

42:3

PA_BIT42_3

R

Physical address bit 42:3. Contains the value indicated by

ASI_AFAR_U2.CONTENTS

, as shown below:

Others Reserved

R

Always read as 0.

All

W

Any write access sets all fields in this register to 0. That is, when a program

writes to

ASI_AFAR_U2

, the entire

ASI_AFAR_U2

is set to 0 regardless of the

write value; any error recorded in

ASI_AFAR_U2

is expunged.

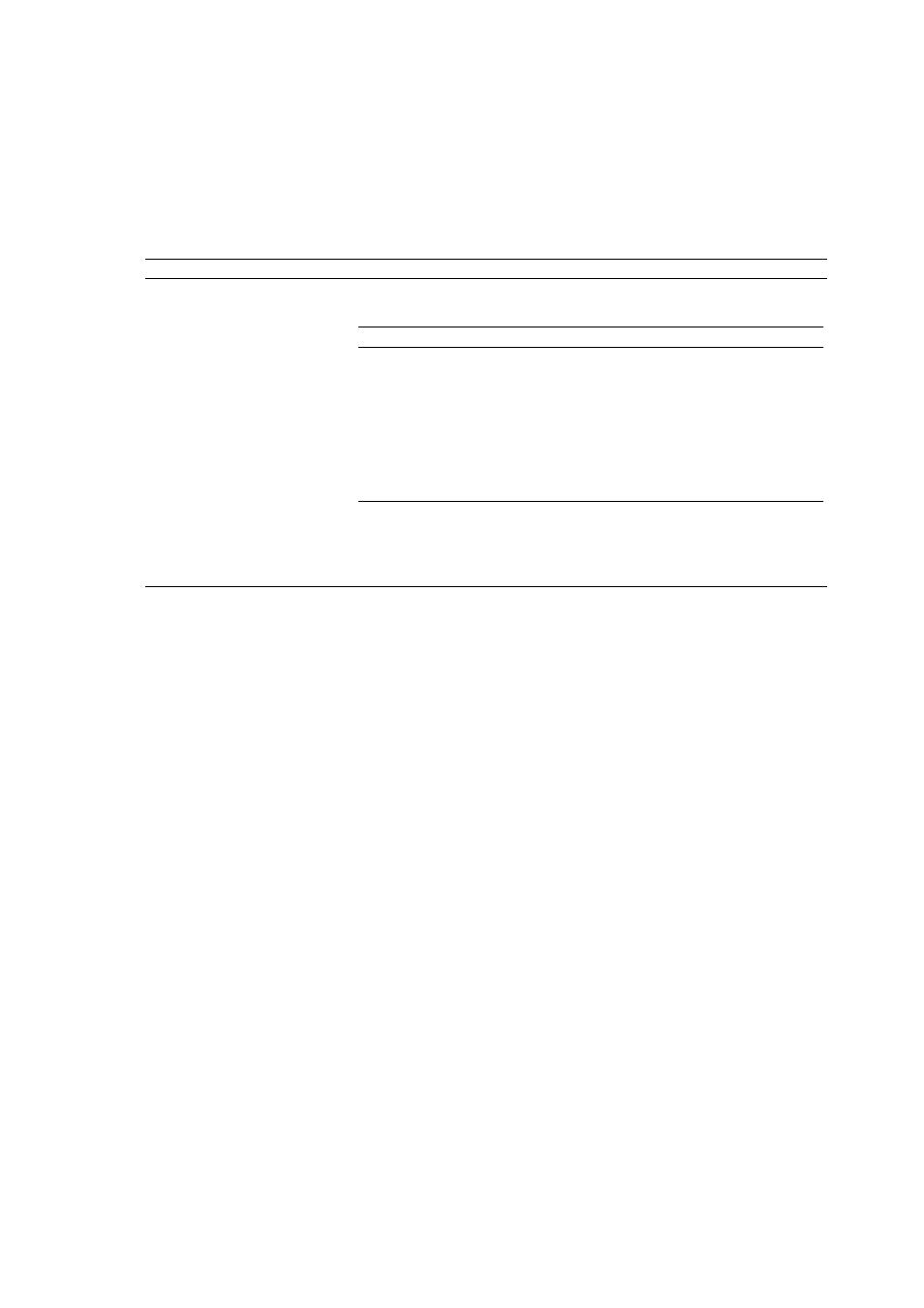

TABLE P-17

ASI_ASYNC_FAULT_ADDR_U2

(

ASI_AFAR_U2

) Register Bit Description (Continued)

Bit

Name

R/W

Description

ASI_AFAR_U2.CONTENTS

Error Name

Contents of

PA_BIT42_3

40

16

CE_INCOMED

The physical address of the

doubleword with the error.

80

16

UE_RAW_L2$FILL

The physical address of the

doubleword with the error.

C0

16

UE_RAW_L2$INSD

The physical address of the

cache line (64-byte block) with

the error. The least significant 3

bits in the

PA_BIT42_3

field

are invalid and unpredictable.