2 instruction formats and fields, Instruction formats and fields 28 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 39

28

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

6.2

Instruction Formats and Fields

Instructions are encoded in five major 32-bit formats and several minor formats.

Please refer to Section 6.2 of Commonality for illustrations of four major formats.

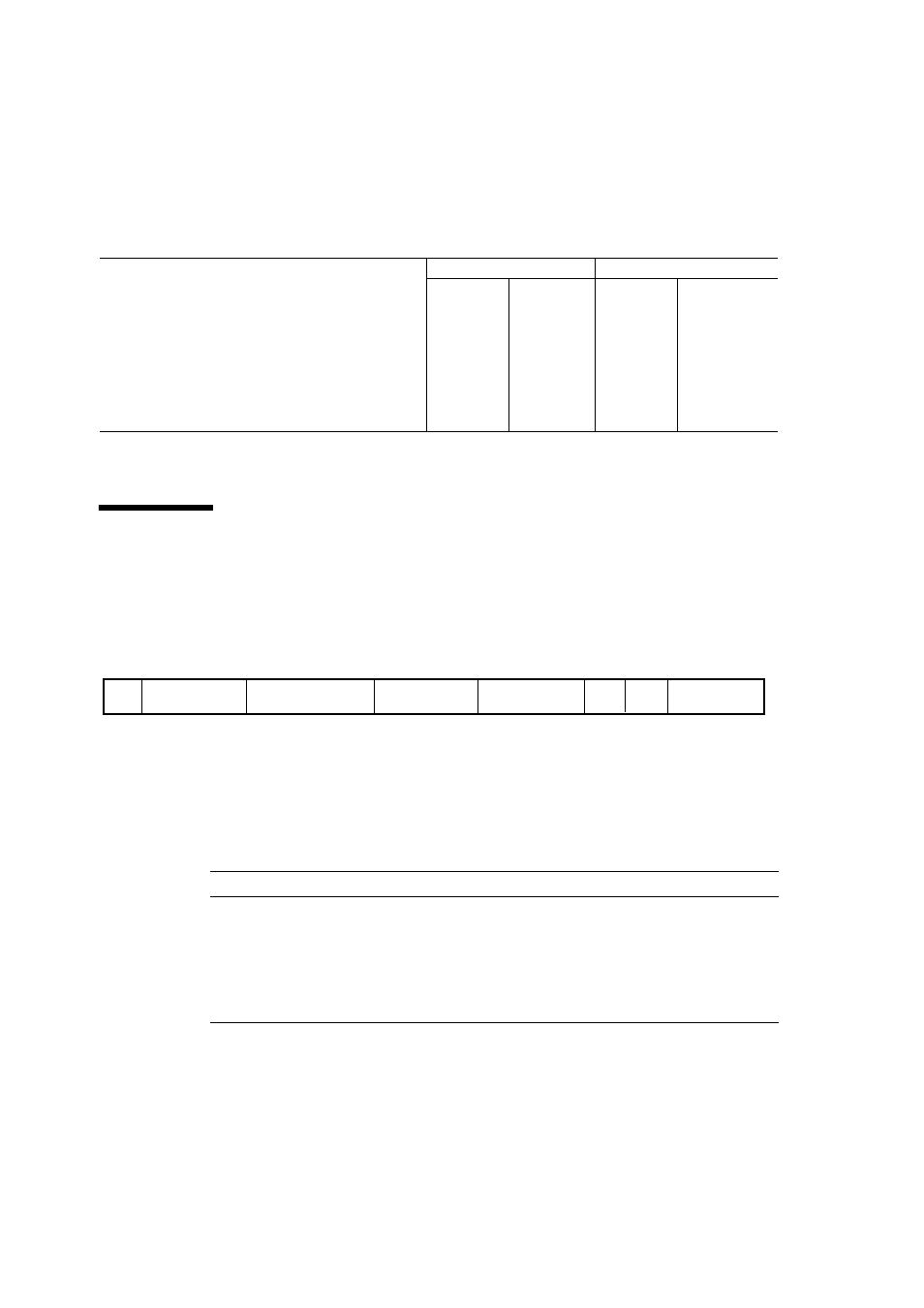

illustrates Format 5, unique to SPARC64 V.

FIGURE 6-1

Summary of Instruction Formats: Format 5

Instruction fields are those shown in Section 6.2 of Commonality. Three additional

fields are implemented in SPARC64 V. They are described in

STDA

Yes

STDFA

Yes

STFSR

,

STXFSR

Yes

Tcc

Yes

Yes

Yes

WRASR

Yes

2

Yes

1. When

#

cmask !

=

0

.

2.

WRGSR

only.

TABLE 6-2

Instruction Fields Specific to

SPARC64 V

Bits

Field

Description

13:9

rs3

This 5-bit field is the address of the third

f

register source operand for

the floating-point multiply-add and multiply-subtract instruction.

8.7

var

This 2-bit field specifies which specific operation (variation) to perform

for the floating-point multiply-add and multiply-subtract instructions

6.5

size

This 2-bit field specifies the size of the operands for the floating-point

multiply-add and multiply-subtract instructions.

TABLE 6-1

SPARC64 V Syncing Instructions (Continued)

Opcode

Presyncing

Postsyncing

Sync?

Wait for

store global

visibility?

Sync?

Discard

prefetched

instructions?

op3

rd

op

rs1

rs3

rs2

var

Format 5 (op = 2, op3 = 37

16

):

FMADD

,

FMSUB

,

FNMADD

, and

FNMSUB

(in place of

IMPDEP2B)

31

14

19

24

18

13 12

5

4

0

25

30 29

11 10

9

7

6

17

8

size