FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 156

Release 1.0, 1 July 2002

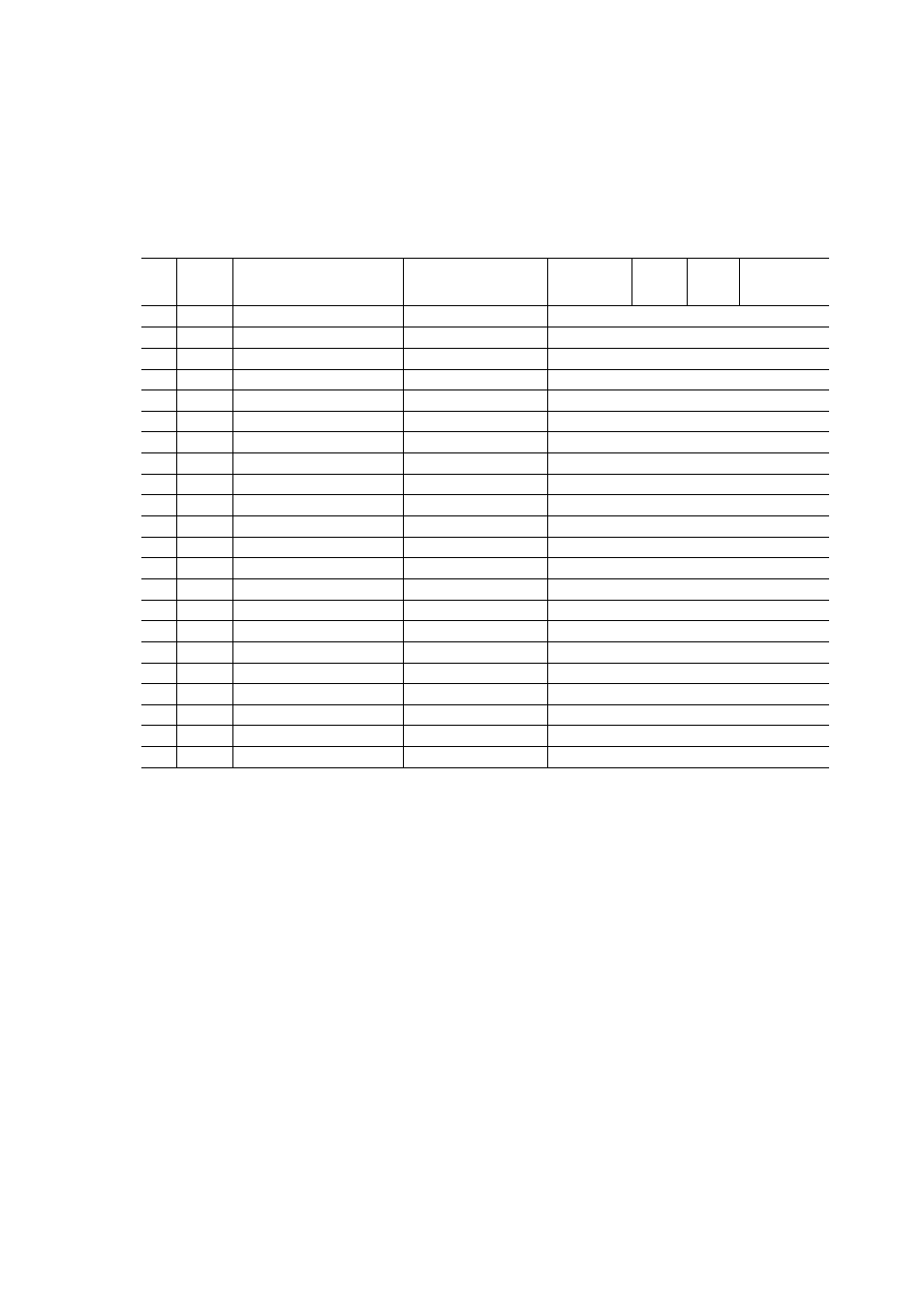

F. Chapter O

Reset, RED_state, and error_state

145

58

20

DMMU_SFAR

Unknown/Unchanged

Unchanged

58

28

DMMU_TSB_BASE

Unknown/Unchanged

Unchanged

58

30

DMMU_TAG_ACCESS

Unknown/Unchanged

Unchanged

58

38

DMMU_VA_WATCHPOINT

Unknown/Unchanged

Unchanged

58

40

DMMU_PA_WATCHPOINT

Unknown/Unchanged

Unchanged

58

48

DMMU_TSB_PEXT

Unknown/Unchanged

Unchanged

58

58

DMMU_TSB_NEXT

Unknown/Unchanged

Unchanged

59

—

DMMU_TSB_8KB_PTR

Unknown/Unchanged

Unchanged

5A

—

DMMU_TSB_64KB_PTR

Unknown/Unchanged

Unchanged

5B

—

DMMU_TSB_DIRECT_PTR

Unknown/Unchanged

Unchanged

5C

—

DTLB_DATA_IN

Unknown/Unchanged

Unchanged

5D

—

DTLB_DATA_ACCESS

Unknown/Unchanged

Unchanged

5E

—

DTLB_TAG_READ

Unknown/Unchanged

Unchanged

5F

—

DMMU_DEMAP

Unknown/Unchanged

Unchanged

60

—

IIU_INST_TRAP

0

Unchanged

6E

—

EIDR

0/Unchanged

Unchanged

6F

—

BARRIER_SYNC_P

Unknown/Unchanged

Unchanged

77

40:68

INTR_DATA0:5_W

Unknown/Unchanged

Unchanged

77

70

INTR_DISPATCH_W

Unknown/Unchanged

Unchanged

77

80:88

INTR_DATA6:7_W

Unknown/Unchanged

Unchanged

7F

40:88

INTR_DATA0:7_R

Unknown/Unchanged

Unchanged

EF

—

BARRIER_SYNC

Unknown/Unchanged

Unchanged

1.Hard POR occurs when power is cycled. Values are unknown following hard POR. Soft POR occurs when

UPA_RESET_L is asserted. Values are unchanged following soft POR

2.The first watchdog timeout trap is taken in execute_state (i.e.

PSTATE.RED

= 0), subsequent watchdog timeout

traps as well as watchdog traps due to a trap @

TL

=

MAX_TL

are taken in

RED_state

. See Section O.1.2, Watchdog

Reset (WDR), on page 138 for more details.

TABLE O-3

ASI Register State After Reset and in

RED_state

(3 of 3)

A

S

I

VA

Name

POR

1

WDR

2

XIR

SIR

RED_state