P.8.3 asi register error handling, Asi register error handling 183 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 194

Release 1.0, 1 July 2002

F. Chapter P

Error Handling

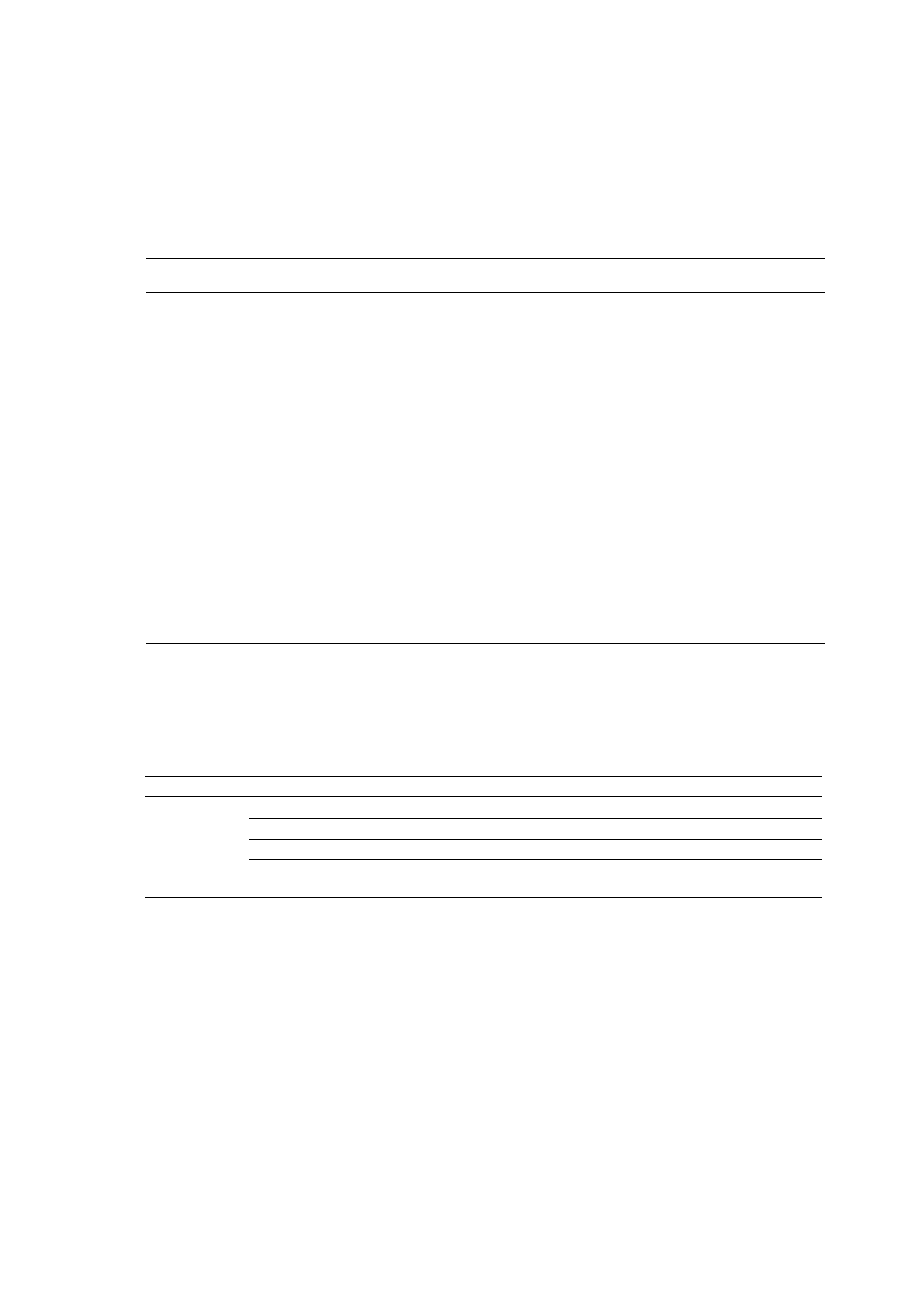

183

P.8.3

ASI Register Error Handling

The terminology used in

is defined as follows:

5

PC

R

Parity

Always

IUG_PSTATE

ADE

trap

6

FPRS

RW

Parity

Always

IUG_%F

ADE

trap, W

7

—

8-15

—

16

PCR

RW

None

—

—

—

17

PIC

RW

None

—

—

—

18

DCR

R

None

—

—

—

19

GSR

RW

Parity

Always

IUG_%F

ADE

trap, W

20

SET_SOFTINT

W

None

—

—

—

21

CLEAR_SOFTINT

W

None

—

—

—

22

SOFTINT

RW

Parity

AUG

always

InstAccess

(I)AUG_CRE

I(A)UG_CRE

W

W

23

TICK_COMPARE

RW

None

—

—

—

24

STICK

RW

Parity

AUG

always

InstAccess

(I)AUG_CRE

I(A)UG_CRE

W

W

25

STICK_COMPARE

RW

Parity

AUG

always

InstAccess

(I)AUG_CRE

I

(A)UG_CRE

W

W

(1 of 3)

Column

Term

Meaning

Error Protect

Parity

Parity protected.

ECC

ECC (double-bit error detection, single-bit error correction) protected.

Gecc

Generated ECC.

PP

Parity propagation. The parity error in the input registers to calculate the

register value is propagated.

TABLE P-19

ASR Error Handling (Continued)

ASR

Number Register Name

RW

Error Protect

Error Detect Condition

Error Type

Correction