F.11 mmu bypass, Mmu bypass 104 – FUJITSU Implementation Supplement Fujitsu SPARC64 V User Manual

Page 115

104

SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

F.11

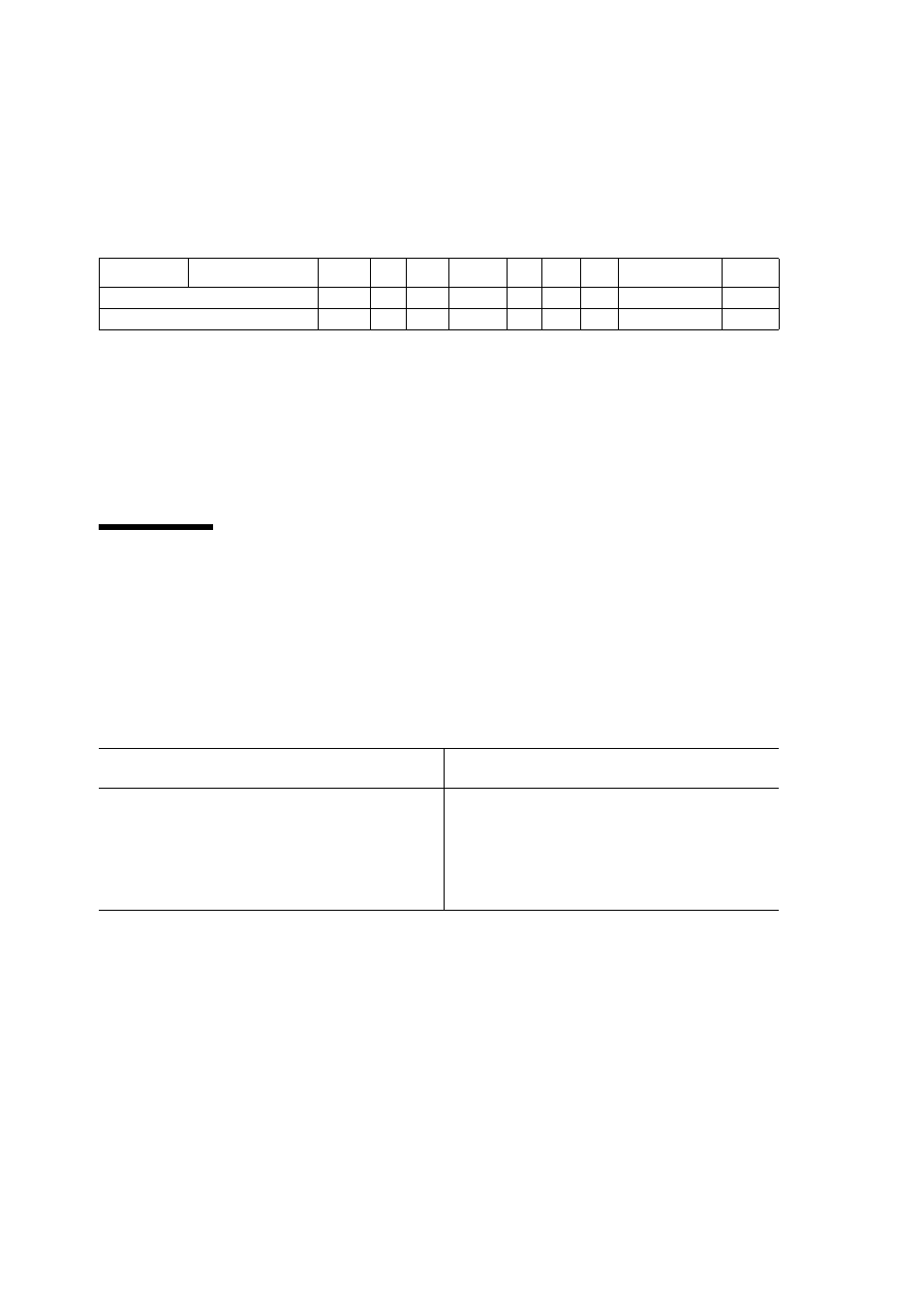

MMU Bypass

On SPARC64 V, two additional ASIs are supported as DMMU bypass accesses:

ASI_ATOMIC_QUAD_LDD_PHYS

(ASI 34

16

) and

ASI_ATOMIC_QUAD_LDD_PHYS_LITTLE

(ASI 3C

16

)

shows the bypass attribute bits on SPARC64 V. The first four rows

conform to the bypass attribute bits defined in

TABLE

F-15 of Commonality.

Miss on fault/exception

K

1

K

K

K

1

K

K

K

Miss on miss

K

K

K

U

K

1

K

K

K

1.

The value of

DSFSR.CT

is 11 when the ASI is not a translating ASI. The value 11 is recorded in

DSFSR.CT

for

an illegal value in ASI (00

16

–03

16

, 12

16

–13

16

, 16

16

–17

16

, 1A

16

–1B

16

, 1E

16

–23

16

, 2D

16

–2F

16

, or 35

16

–3B

16

).

2.

Valid only for the

data_access_error

caused by

DSFSR.UE

or

DSFSR.UPA

.

3.

Types: 0 – logic 0; 1 – logic 1; V – Valid field to be updated; “—” – not a valid field

4.

Memory reference instruction only.

5.

Updated when

mDTLB

is signified.

6.

Types: 0 – logic 0; 1 – logic 1; V– Valid field to be updated; “—” – not a valid field

7.

Fault/exception on miss means the miss happened first, then a fault/exception was encountered before soft-

ware had a chance to clear the

DSFSR

register.

TABLE F-11

Bypass Attribute Bits

on SPARC64 V

ASI

ASI

Attribute Bits

NAME

VALUE CP

IE

CV

E

P

W

NFO

Size

ASI_PHYS_USE_EC

ASI_PHYS_USE_EC_LITTLE

14

16

1C

16

1

0

0

0

0

1

0

8 Kbytes

ASI_PHYS_BYPASS_EC_WITH_EBIT

ASI_PHYS_BYPASS_EC_WITH_EBIT_LITTLE

15

16

1D

16

0

0

0

1

0

1

0

8 Kbytes

ASI_ATOMIC_QUAD_LDD_PHYS

ASI_ATOMIC_QUAD_LDD_PHYS_LITTLE

34

16

3C

16

0

0

1

0

0

0

0

8 Kbytes

TABLE F-10

DSFSR

Update Policy

Field

TLB#,

index

FV

OW

W, PR,

NF, CT

1

FT

TM

ASI

UE, UPA,

mDTLB, NC

2

, E

2

DSFAR