Chapter 2 systemverilog api overview, Figure 2-1. systemverilog bfm internal structure – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

Page 27

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

27

April 2014

Chapter 2

SystemVerilog API Overview

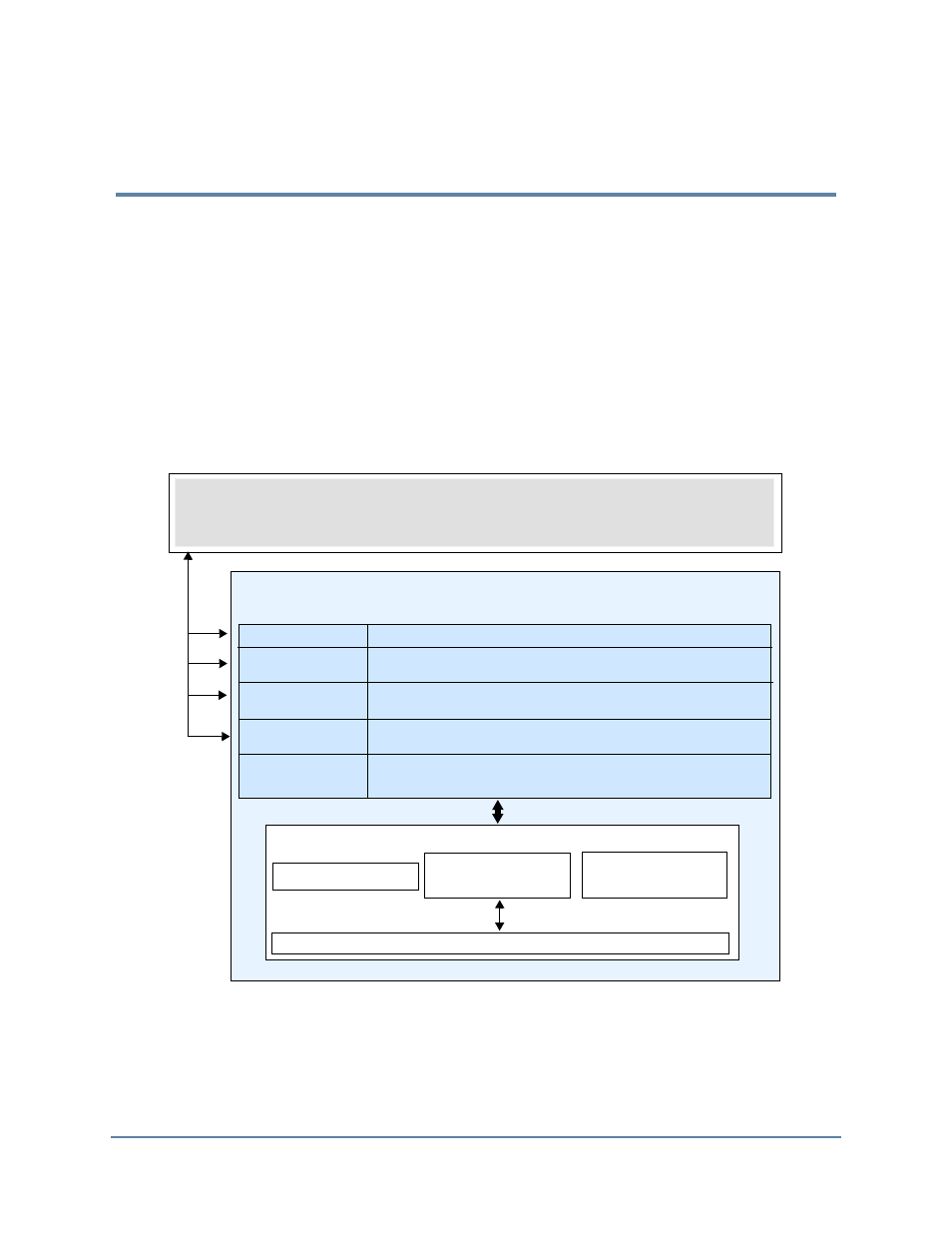

This chapter provides the functional description of the SystemVerilog (SV) Application

Programming Interface (API) for all BFM (master, slave, and monitor) components. For each

BFM, you can configure the protocol transaction fields that are executed on the protocol signals,

as well as control the operational transaction fields that permit delays to be introduced between

the handshake signals for each of the five address, data, and response channels.

In addition, each BFM API has tasks that wait for certain events to occur on the system clock

and reset signals, and tasks to get and set information about a particular transaction.

Figure 2-1. SystemVerilog BFM Internal Structure

SystemVerilog BFM API

Configuration

Creating

Transaction

Waiting Events

Executing

Transaction

Access

Transaction

create*_transaction

1

set_config/get_config

wait_on

get*_phase

3

Rx_Transaction

queue

queue

Tx_Transaction

Configuration

Wire level

Notes: 1. Refer to

2. Refer to

execute_transaction(), execute*_phase()

3. Refer to

get_rw_transaction/get*_phase

3

get*_addr/get*_data

3

execute_transaction, execute*_phase

2

SystemVerilog interface

Test Program SystemVerilog