Axi read transaction master and slave roles, Figure 1-3. slave write transaction phases, Figure 1-3 – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

Page 25

Mentor VIP Altera Edition

AXI4-Lite Transactions

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

25

April 2014

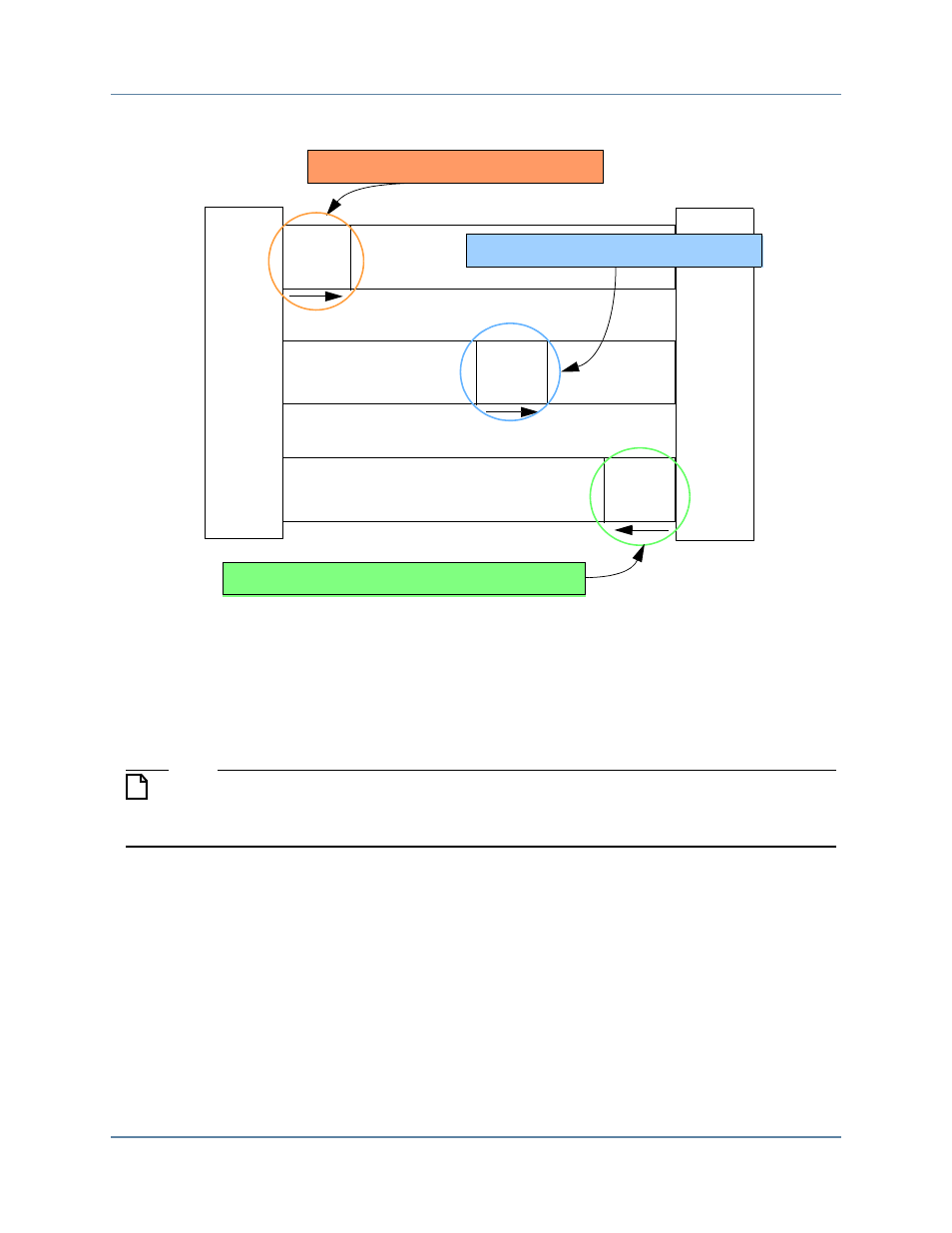

Figure 1-3. Slave Write Transaction Phases

The slave then executes a write response phase by calling the

execute_write_response_phase()

task and completes its role in the write transaction.

AXI Read Transaction Master and Slave Roles

Note

The following description of a read transaction references the SystemVerilog BFM API

tasks. There are equivalent VHDL BFM API procedures that perform the same

functionality.

A read transaction is similar to a write transaction. The master initiates the read by calling the

and

tasks. The execute_transaction() calls the

the

task as illustrated

Master

interface

Slave

interface

Write

data

Write response channel

Write data channel

Write address channel

Write

response

Address

and

control

execute_write_response_phase() - Slave

get_write_data_phase() - Slave

get_write_addr_phase() - Slave