Rockwell Automation 20D PowerFlex 700S AC Drives with Phase II Control Reference Manual User Manual

Page 135

Rockwell Automation Publication PFLEX-RM003E-EN-E - January 2011

135

Detailed Drive Operation Chapter 1

• Bits 10…12 “SmplRate btx” configure the sample interval for measuring

below). Increasing the encoder sample interval

improves speed measurement near zero speed. Decreasing allows the speed

control regulator to perform with high gains at high speeds.

• The remaining bits are reserved (not used).

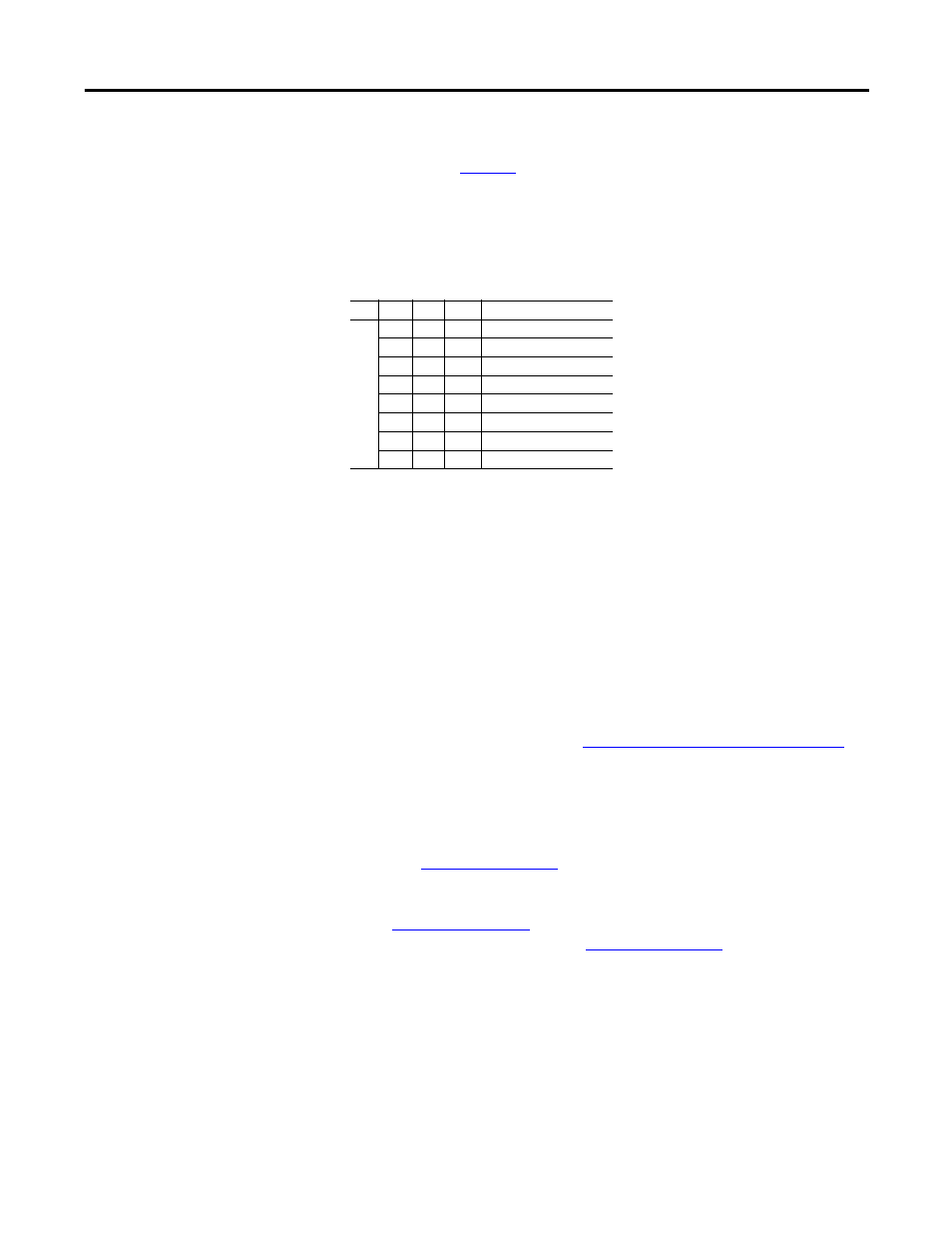

Table 18 - FIR Filter Settings

Resolver Feedback Option

The position feedback (seen in parameter 250 [FB Opt0 Posit]) from a resolver

counts at a rate of 65,536 counts per motor revolution.

Parameter 251 [FB Opt0 Spd Fdbk] contains the speed feedback from the

resolver when connected at port 0.

Parameter 268 [Resolver0 Config] is used to configure the Resolver feedback

option card. The bits for [Resolver0 Config] are defined as follows:

• Setting bit 0 “Cable Tune” enables the cable tuning test, resetting the bit to

zero disables the test. Refer to

Resolver Cable Tuning Tests on page 138

for

more information.

• Bit 1 is reserved (not used).

• Bits 2 “Resolution 0” and 3 “Resolution 1” select the resolver resolution

(see

). The resolution setting determines the number

of significant bits that are calculated in parameter 250 [FB Opt0 Posit]. It

does not affect the number of counts created per resolver revolution (see

). However, the resolution sets a limit on the

maximum tracking speed (see

).

• Setting bit 4 “Energize” energizes the resolver, resetting the bit to zero de-

energizes the resolver.

• Bit 5 “Resolver Dir” determines the counting direction. If set to “0”,

direction is forward or up. If set to “1”, the direction is reverse or down.

Bit 12

11

10

Number of Taps

0

0

0

1

0

0

1

2

0

1

0

4

0

1

1

8

1

0

0

16

1

0

1

32

1

1

0

64

1

1

1

127