Chapter 7, Sdram controller, Introduction – Cirrus Logic EP73xx User Manual

Page 81: Features, Sdram register list, Chapter 7. sdram controller, Introduction -1 features -1 sdram register list -1, Table 7-1: sdram registers -1, Chapter 7 7 sdram controller introduction

EP7309/11/12 User’s Manual - DS508UM4

7-1

Copyright Cirrus Logic, Inc. 2003

77

7

Chapter 7

7

SDRAM Controller

Introduction

External SDRAM on the EP7311 and EP7312 is supported via the SDRAM controller.

It allows industry standard SDRAM memories to be used within the address space of

the EP73xx with no software overhead. The controller is attached to the ARM core

through the internal high speed bus. It operates at a maximum clock speed of

36.864 MHz (45 MHz when is CPU running at 90 MHz), providing all the necessary

connections to interface to two banks of SDRAM. For information on implementing

external SDRAM with the EP7312, see the Application Note,

. The EP7309 does not include the SDRAM controller.

Features

The SDRAM controller within the EP7311 and EP7312 provides a convenient method

for using inexpensive SDRAM devices as local memory.

It supports:

• Standard NEC or compatible devices in sizes of 16 to 256 Mbit, yielding a

total memory capacity of 2 to 64 MByte

• Up to two external banks of SDRAM

SDCS[0:1]

, and control of four

internal banks for each SDRAM device.

• A programmable bus width for accessing 16 or 32 bit wide banks

• Putting the SDRAM devices into self-refresh mode when the CPU is put

into Standby

• Quad word or quad halfword accesses with byte mask selects for short

reads

• Internal multiplexing of address lines for contiguous memory access

• Automatic JEDEC Standard No. 21-C compliant SDRAM initialization

SDRAM Register List

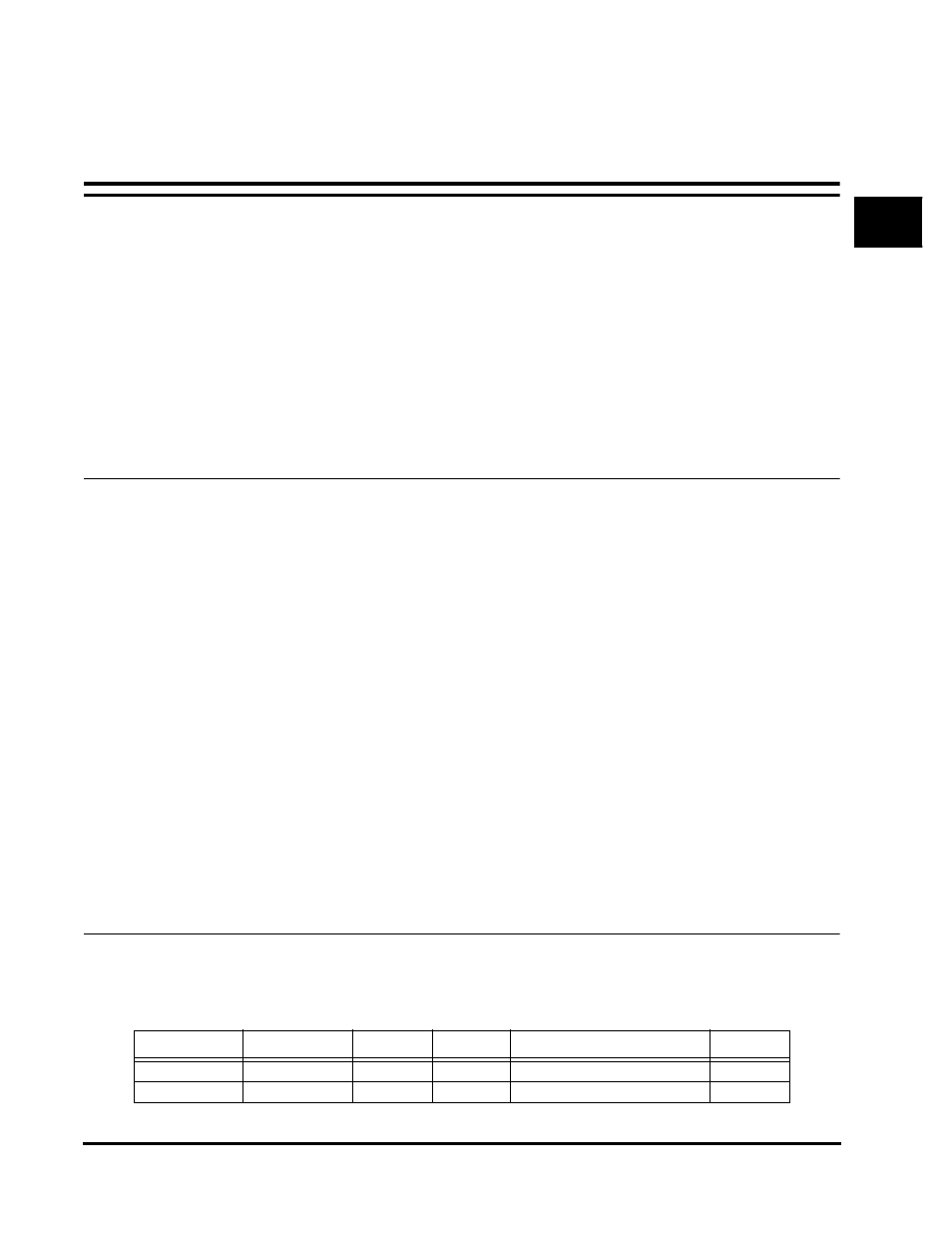

Table 7-1: SDRAM Registers

Address

Name

Type

Size

Description

Page

0x8000.2300

SDCONF

R/W

16

SDRAM Control Register

0x8000.2340

SDRFPR

R/W

16

SDRAM Refresh Period Register