Pin description, Pin description -6 – Cirrus Logic EP73xx User Manual

Page 20

1-6

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

Introduction

1

Pin Description

describes the function of all external signals to the EP73xx. Note

that all output signals and all I/O pins (when acting as outputs) are High-Z capable.

This is to enable the High-Z test modes to be supported.

0x8000.22C0

LEDFLSH

0

RW

7

LED Flash register

0x8000.2300

SDCONF

2

RW

32

SDRAM Configuration Register

0x8000.2340

SDRFPR

128

RW

16

SDRAM Refresh Register

0x8000.2440

UNIQID

0

R

32

32-bit unique ID for the EP73xx device

0x8000.2600

DAI64Fs

0

RW

32

DAI 64Fs Control Register

0x8000.2610

PLLW

W

8

Write Register for PLL Multiplier

0x8000.A5A8

PLLR

R

Read Register for PLL Multiplier

0x8000.2700

RANDID0

0

R

32

Bits 31-0 of 128-bit random ID for the EP73xx device

0x8000.2704

RANDID1

0

R

32

Bits 63-32 of 128-bit random ID for the EP73xx device

0x8000.2708

RANDID2

0

R

32

Bits 95-64 of 128-bit random ID for the EP73xx device

0x8000.270C

RANDID3

0

R

32

Bits 127-96 of 128-bit random ID for the EP73xx device

All other address

space that is not

assigned to a

register listed in

this table

Reserved

All addresses that are outside the address space of the

registers listed in this table are reserved. The undefined

areas contain test registers used during manufacturing

tests. Writes to this area should never be attempted

during normal operation as this may cause unexpected

behavior. Any read from this register will be undefined.

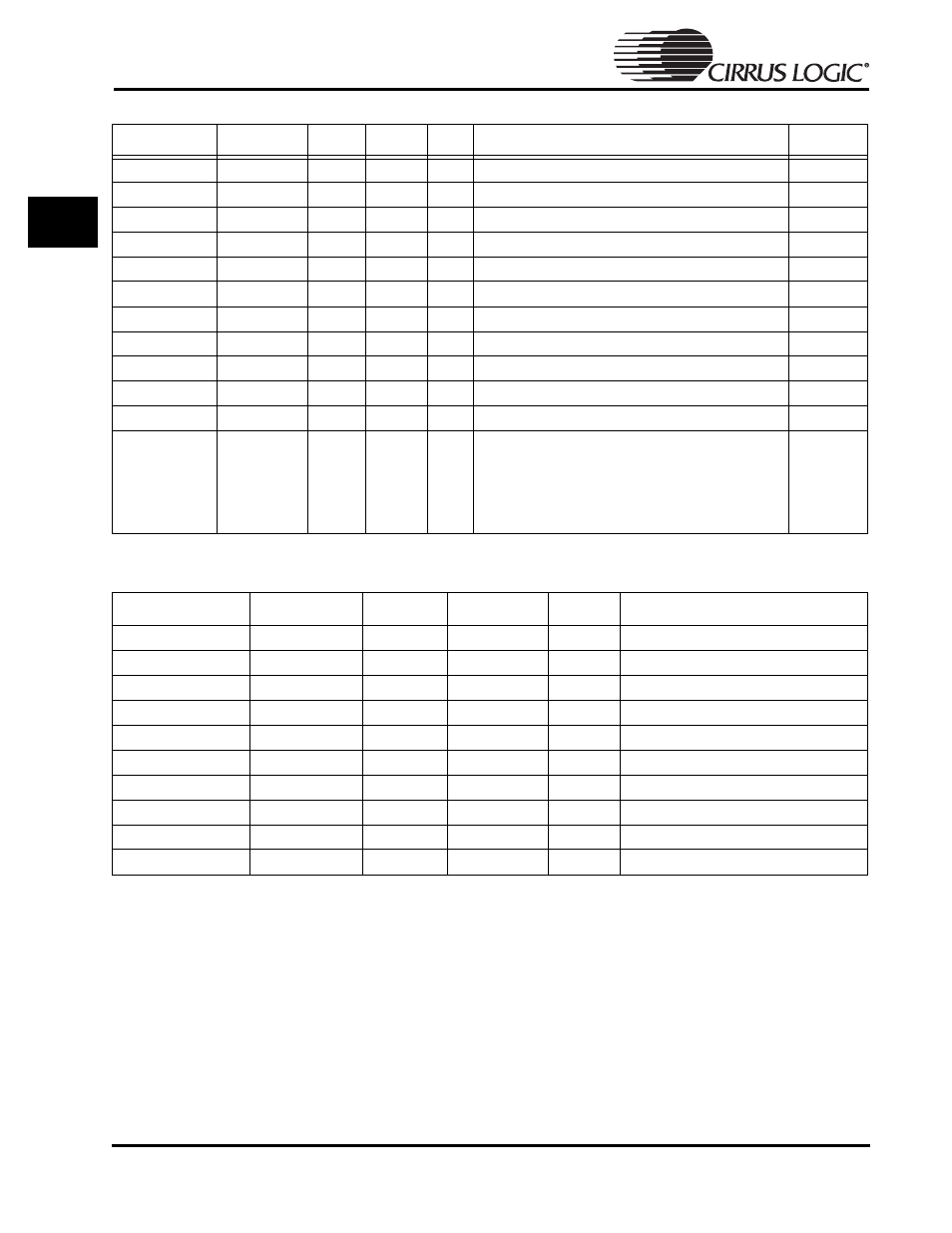

Table 1-3: EP73xx Internal Registers (Big Endian Mode)

Big Endian Mode

Name

Default

RD/WR

Size

Comments

0x0000.0083

PEDR

0

RW

3

Port E Data Register

0X8000.00C3

PEDDR

0

RW

3

Port E Data Direction Register

0x8000.0000

PDDR

0

RW

8

Port D Data Register

0x8000.0001

—

—

8

Reserved

0x8000.0002

PBDR

0

RW

8

Port B Data Register

0x8000.0003

PADR

0

RW

8

Port A Data Register

0x8000.0040

PDDDR

0

RW

8

Port D Data Direction Register

0x8000.0041

—

—

8

Reserved

0x8000.0042

PBDDR

0

RW

8

Port B Data Direction Register

0x8000.0043

PADDR

0

RW

8

Port A data Direction Register

Table 1-2: EP73xx Internal Registers (Little Endian Mode) (Continued)

Address

Name

Default RD/WR

Size

Comments

Page