Uart and sir encoder register descriptions, Uart data registers (uartdr1 and uartdr2), Uart and sir encoder register descriptions -5 – Cirrus Logic EP73xx User Manual

Page 151: Uart data registers (uartdr1 and uartdr2) -5

EP7309/11/12 User’s Manual - DS508UM4

17-5

Copyright Cirrus Logic, Inc. 2003

UART and SIR Encoder

1717

17

UART and SIR Encoder Register Descriptions

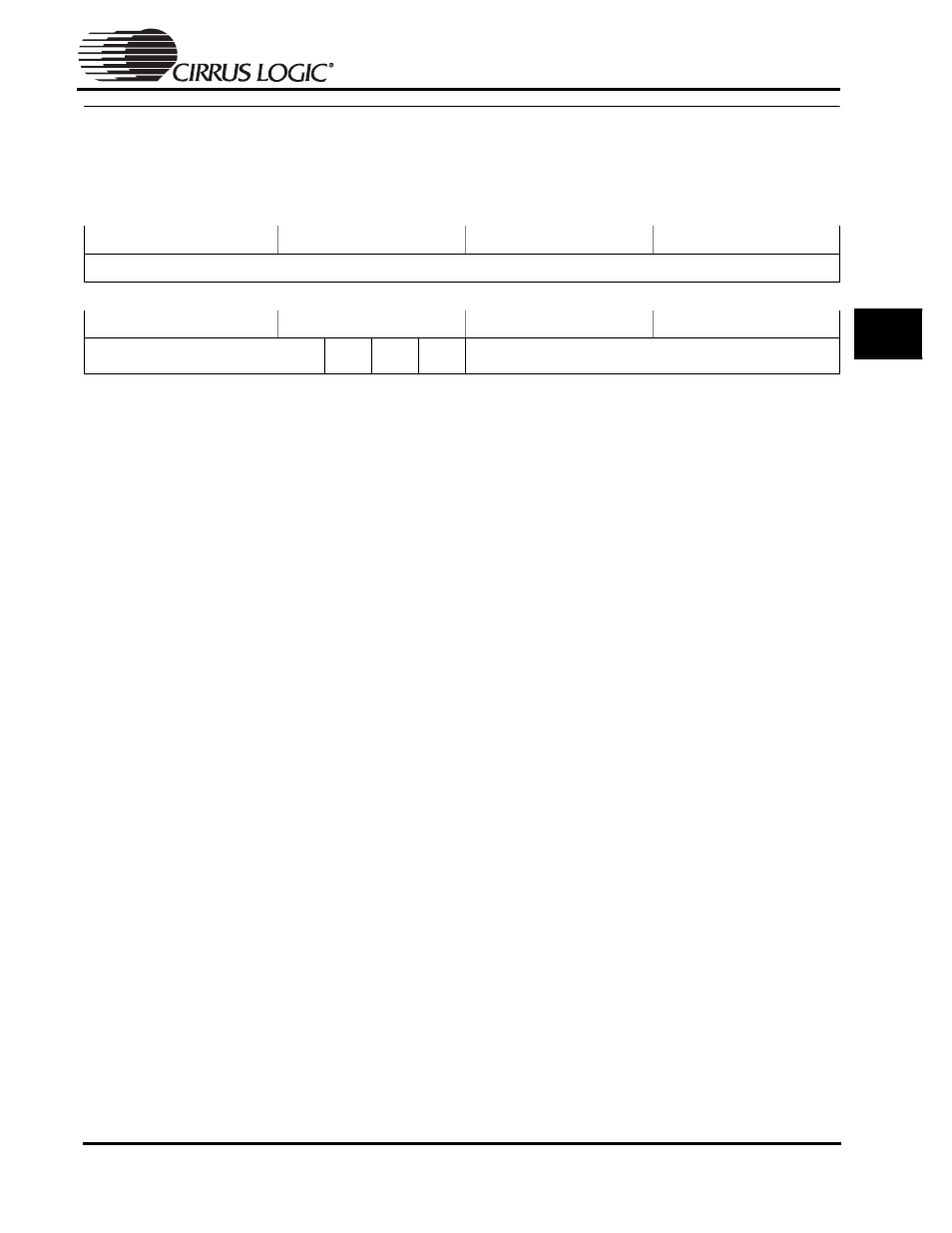

UART Data Registers (UARTDR1 and UARTDR2)

Address:

0x8000.0480 and 0x8000.1480, Read / Write

Bit Descriptions:

RX data:

8-bit data read and write for all data transfers to and from the

FIFOs. Data written to these registers is pushed onto a 16-byte

holding FIFO if enabled. If FIFO is not enabled, one byte is stored

in a 1-byte holding register. Write to this location will initiate

transmission by the UART.

Read data is 8-bits along with three error status bits. If FIFO is

enabled, data read from this register and the error status is

popped from the 16 byte RX FIFO. If FIFO is not enabled, it is read

from data read will be the last byte received by the UART.

FRMERR: UART framing error. This bit is set if the UART detected a framing

error while receiving the associated data byte. Framing errors are

caused by non-matching word lengths or bit rates.

PARERR:

UART parity error. This bit is set if the UART detected a parity

error while receiving the data byte.

OVERR:

UART over-run error. This bit is set if more data is received by the

UART and the FIFO is full. THe overrun is not associated with

any single character and so is not stored in the FIFO. If set, the

entire contents of the FIFO is invalid and should be cleared. This

error bit is cleared by reading the first byte in this register.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

NA

OVERR

PARER

R

FRMER

R

RX data