Dai status register (daisr), Dai status register (daisr) -16, Dai data register 2 (daidr2) – Cirrus Logic EP73xx User Manual

Page 140: Address, Bit descriptions

16-16

EP7309/11/12 User’s Manual - DS508UM4

Copyright Cirrus Logic, Inc. 2003

DAI/CODEC/SSI2

16

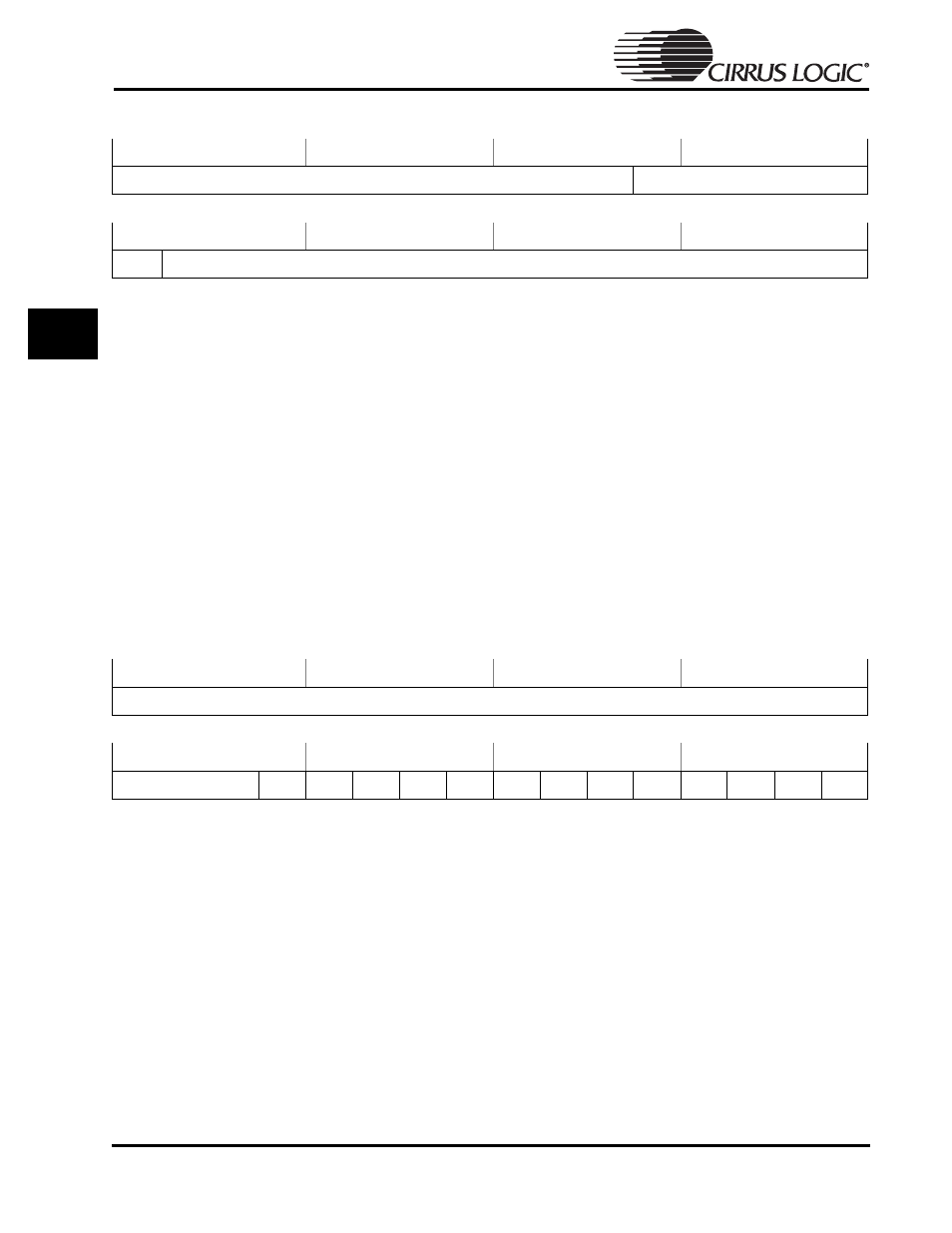

DAI Data Register 2 (DAIDR2)

Address:

0x8000.2080, Read / Write

Bit Descriptions:

FIFOEN:

FIFO Transmit Bit

0 - Disable Transmit, 1 - Enable Transmit

FIFO Channel Select:FIFO Channel Select

01101b - Left channel select, 10001b - Right channel select

DAIDR2 is a 32-bit register that utilizes 21 bits and is used to enable and disable the

FIFOs for the left and right channels of the DAI data stream. The left channel FIFO is

enabled by writing 0x000D.8000 and disabled by writing 0x000D.0000. The right

channel FIFO is enabled by writing 0x0011.8000 and disabled by writing 0x0011.0000.

After writing a value to this register, wait until the FIFO operation complete bit

(FIFO) is set in the DAI status register before writing another value to this register.

DAI Status Register (DAISR)

Address:

0x8000.2100, Read / Write

Bit Descriptions:

(See full bit description for complete details)

RCTS:

Right Channel Transmit FIFO Service Request Flag (read only)

0 - Right Channel Transmit FIFO is more than half full (five entries

or more are filled) or DAI is disabled.

1- Right Channel Transmit FIFO is more than half full or less (four

or fewer entries filled) and the DAI operation is enabled.

RTCM = 1.

RCRS:

Right Channel Receive FIFO Service Request Flag (read only)

0 - Right Channel Receive FIFO is more than half full (five entries

or fewer are filled) or DAI is disabled.

1- Right Channel Receive FIFO is more than half full or less (six or

more entries filled) and the DAI operation is enabled. RTCM = 1.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

FIFO Channel Select

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

FIFOEN

RSVD

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

FIFO

LCNE

LCNF

RCNE

RCNF

LCRO

LCTU

RCRO

RCTU

LCRS

LCTS

RCRS

RCTS